Xilinx 7зі»еҲ—FPGAй…ҚзҪ®пјҲug470пјү

Xilinx 7зі»еҲ—FPGAй…ҚзҪ®пјҲug470пјү

- й…ҚзҪ®жЁЎејҸ

- дёІиЎҢй…ҚзҪ®жЁЎејҸ

- жҺҘеҸЈ

- д»Һ-иҝһжҺҘж–№ејҸ

- дё»-иҝһжҺҘж–№ејҸ

- дёІиЎҢиҸҠиҠұй“ҫпјҲйқһеҗҢж—¶й…ҚзҪ®пјү

- дёІиЎҢй…ҚзҪ®пјҲеҗҢж—¶й…ҚзҪ®пјү

- ж—¶еәҸ

- дё»SPIй…ҚзҪ®жЁЎејҸ

- SPIx1/x2 иҝһжҺҘеӣҫ

- SPIx1жЁЎејҸж—¶еәҸ

- SPIx4 иҝһжҺҘеӣҫ

- SPIж“ҚдҪңжҢҮд»Ө

- ж“ҚдҪңflashз©әй—ҙеӨ§дәҺ128Mb

- SPIй…ҚзҪ®ж—¶еәҸ

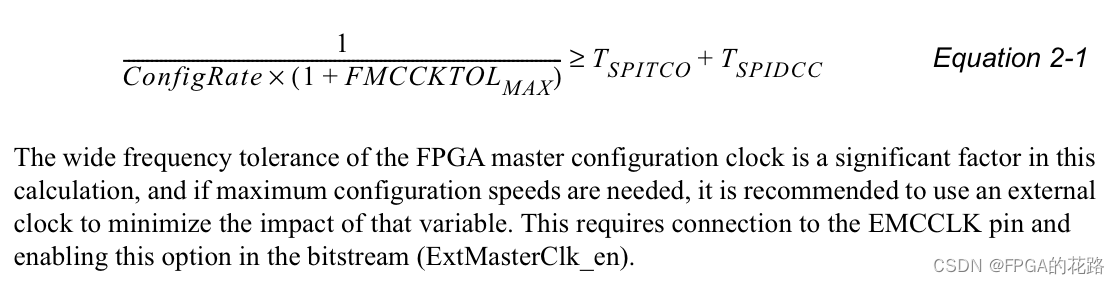

- SPIжңҖеӨ§йҖҹзҺҮи®Ўз®—

- дёҠз”өйЎәеәҸиҰҒжұӮ

- дё»BPIй…ҚзҪ®жЁЎејҸ

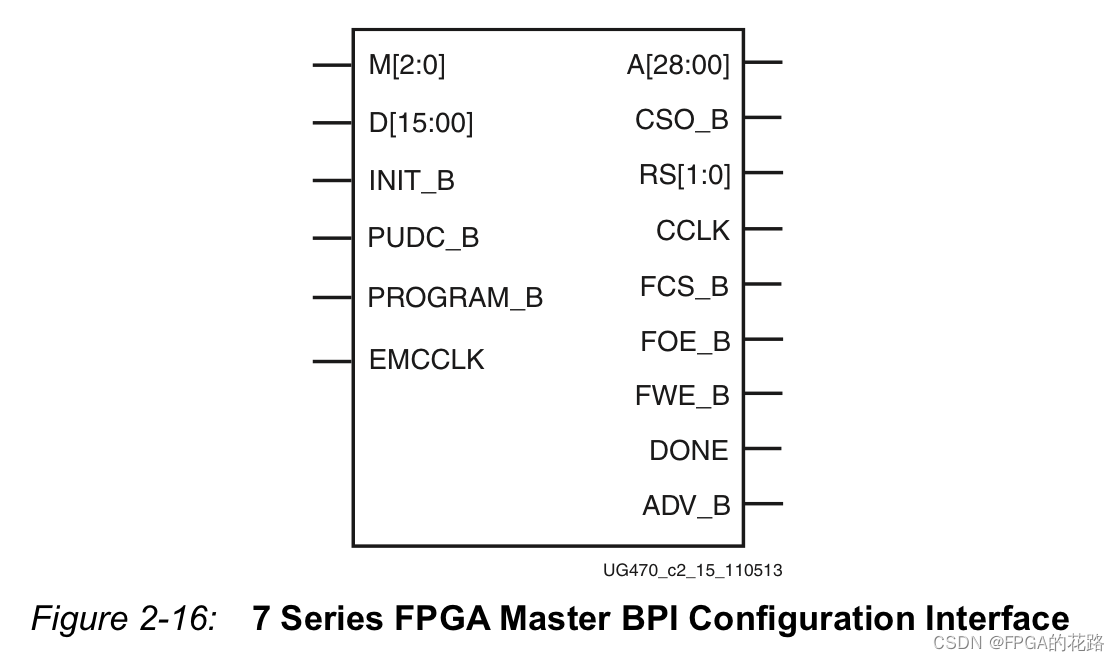

- жҺҘеҸЈ

- ејӮжӯҘиҜ»еҸ–жЁЎејҸ

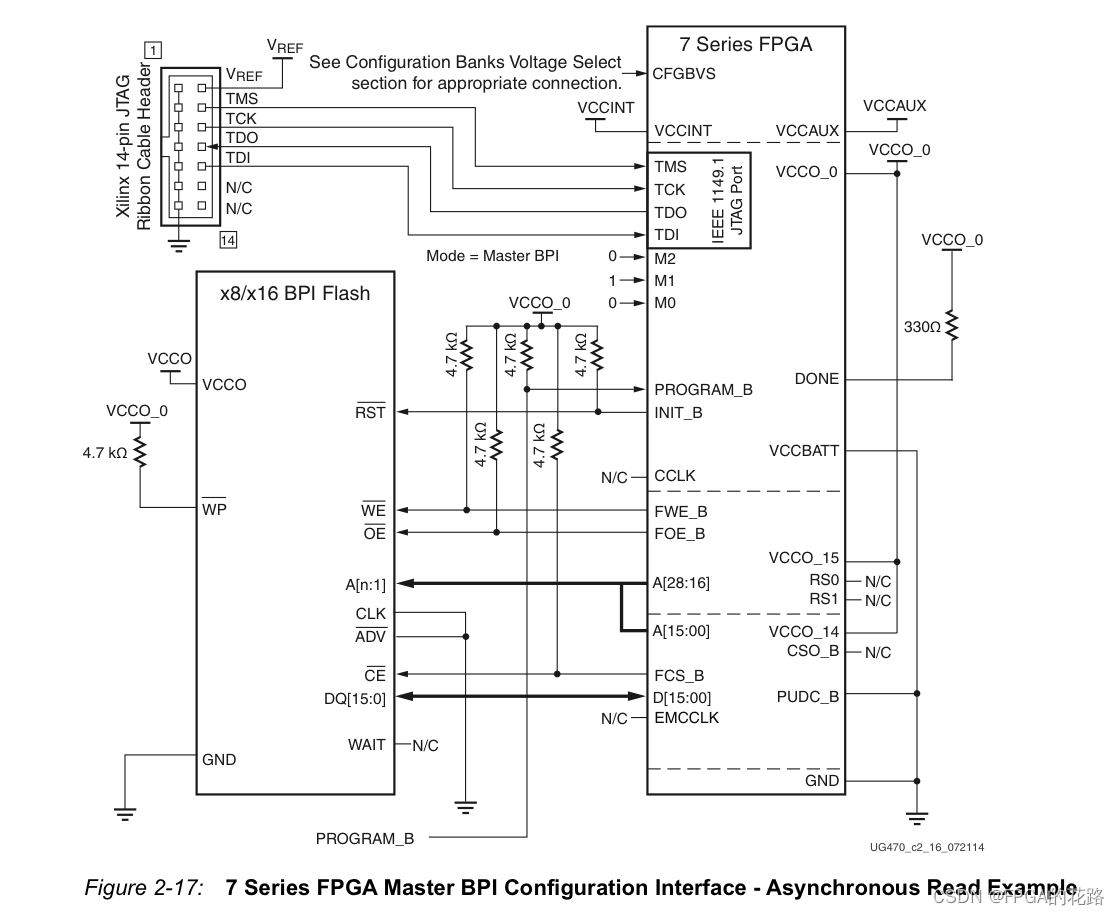

- иҝһжҺҘеӣҫ

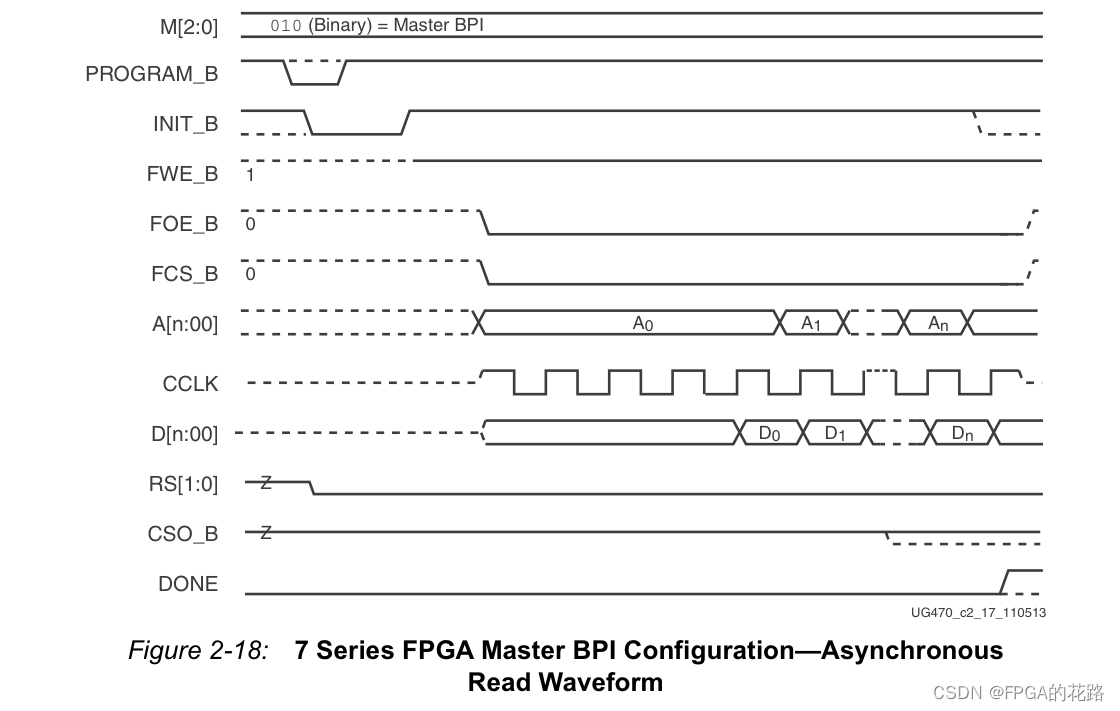

- ж—¶еәҸ

- еҗҢжӯҘиҜ»еҸ–жЁЎејҸ

- иҝһжҺҘеӣҫ

- жңҖеӨ§й…ҚзҪ®йҖҹзҺҮи®Ўз®—

- дёҠз”өйЎәеәҸиҰҒжұӮ

- SelectMAP й…ҚзҪ®жЁЎејҸ

- з®Җд»Ӣ

- жҺҘеҸЈ

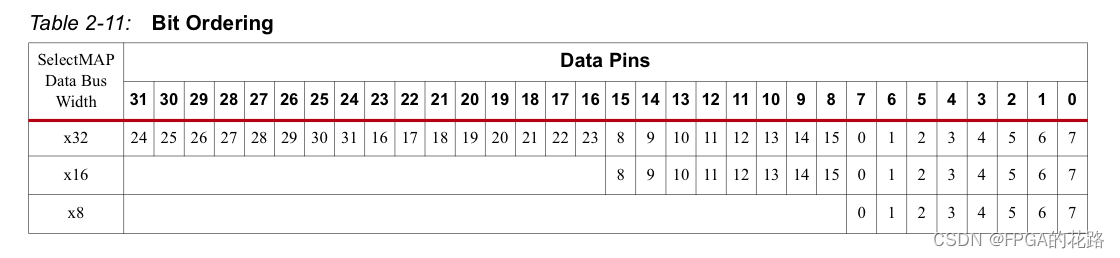

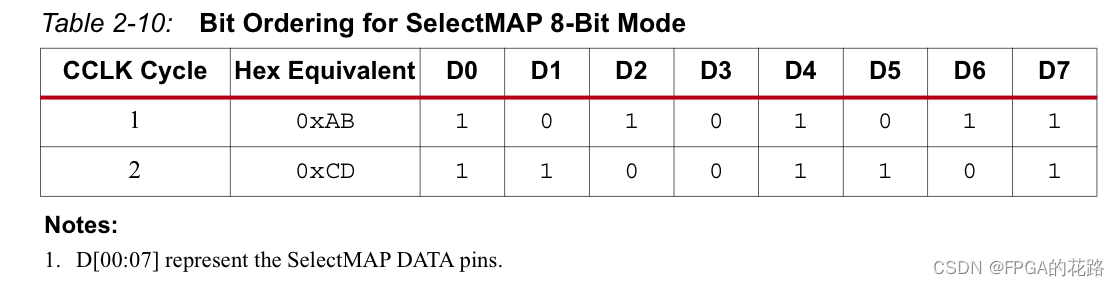

- Data Ordering

- еҚ•еҷЁд»¶й…ҚзҪ®жЁЎејҸ

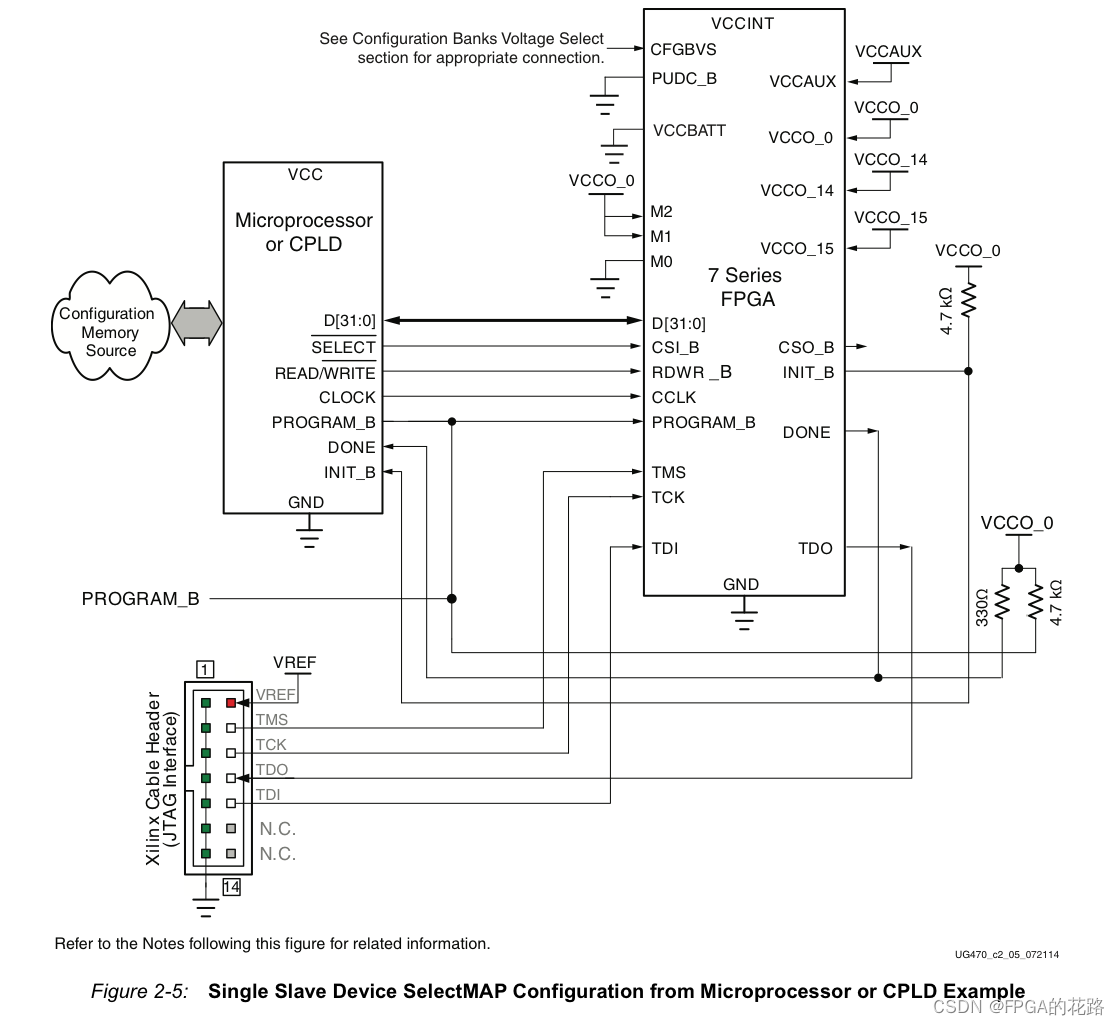

- иҝһжҺҘзӨәдҫӢ

- ж•°жҚ®еҠ иҪҪ

- иҝһз»ӯй…ҚзҪ®ж—¶еәҸ

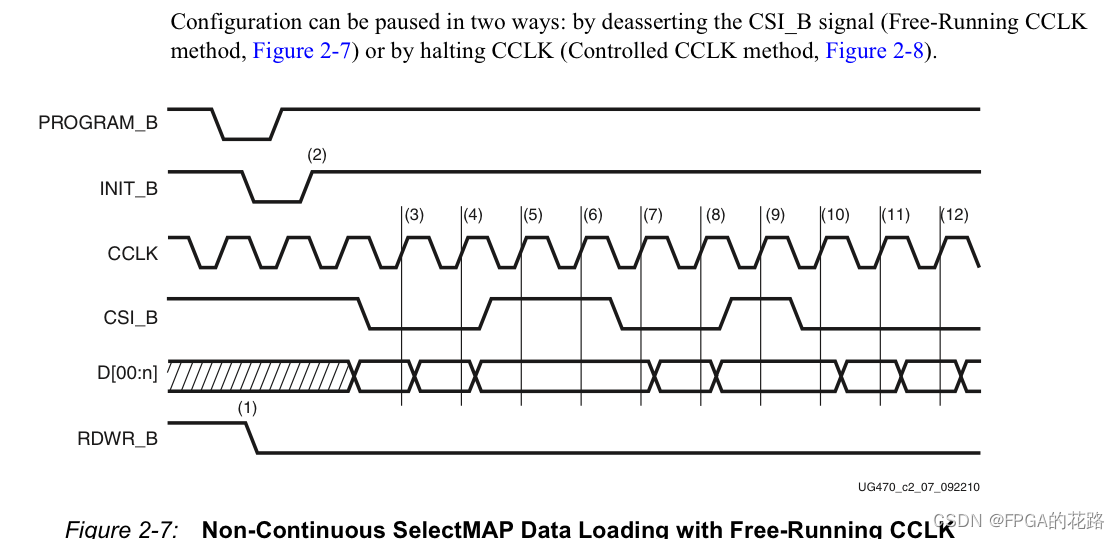

- йқһиҝһз»ӯй…ҚзҪ®ж—¶еәҸ

- з»Ҳжӯўж“ҚдҪң

- ж—¶еәҸ

- зҠ¶жҖҒеӯ—е®ҡд№ү

- зҠ¶жҖҒеӯ—ж•°жҚ®еҜ№йҪҗ

- еӨҡеҷЁд»¶SelectMAPзӢ¬з«Ӣй…ҚзҪ®

- еӨҡеҷЁд»¶SelectMAPеҗҢж—¶й…ҚзҪ®

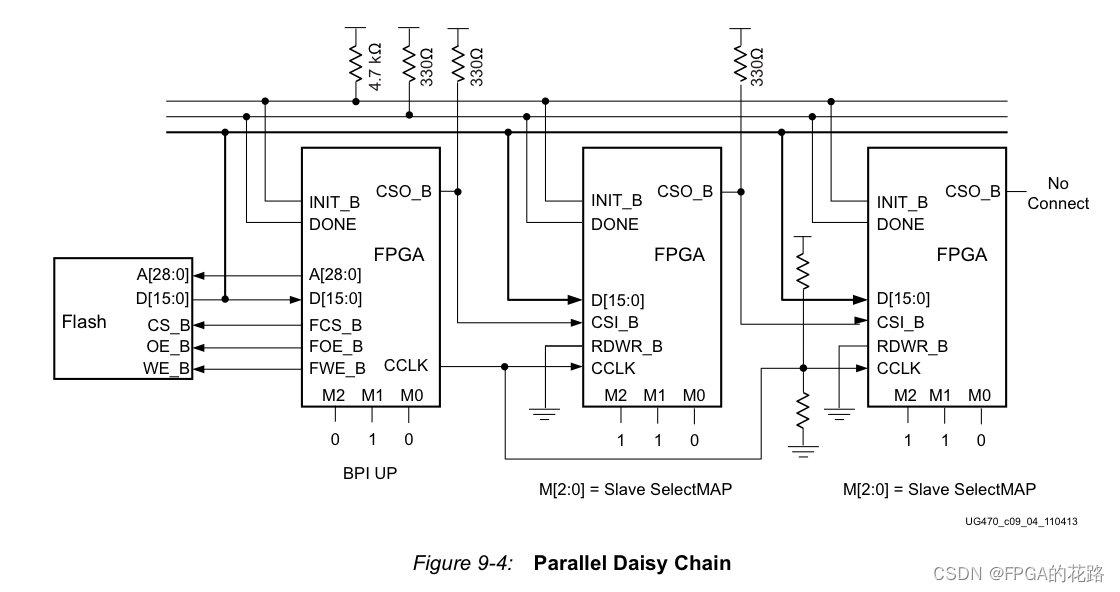

- 并иЎҢиҸҠиҠұй“ҫй…ҚзҪ®

- JTAGй…ҚзҪ®жЁЎејҸ

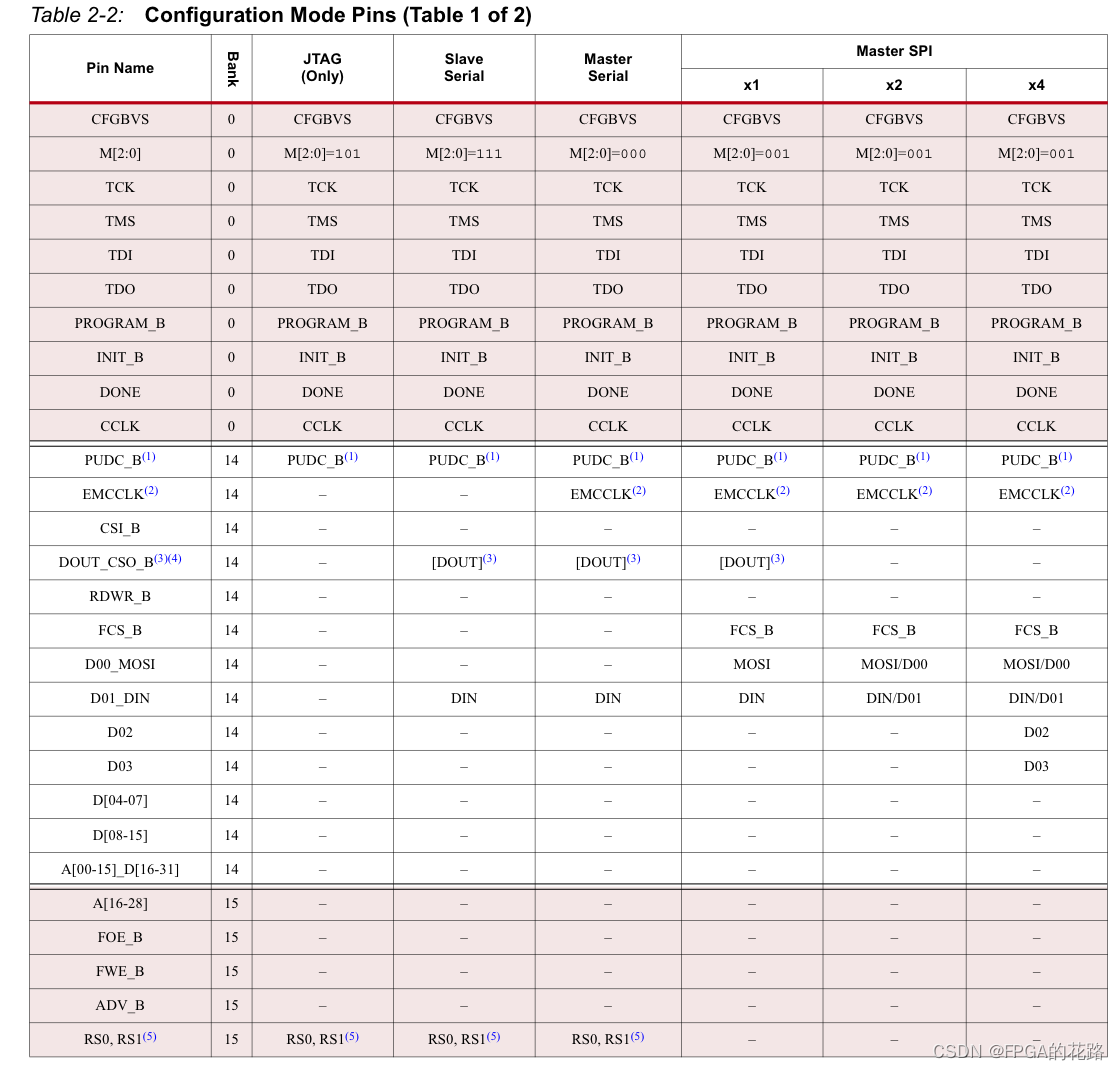

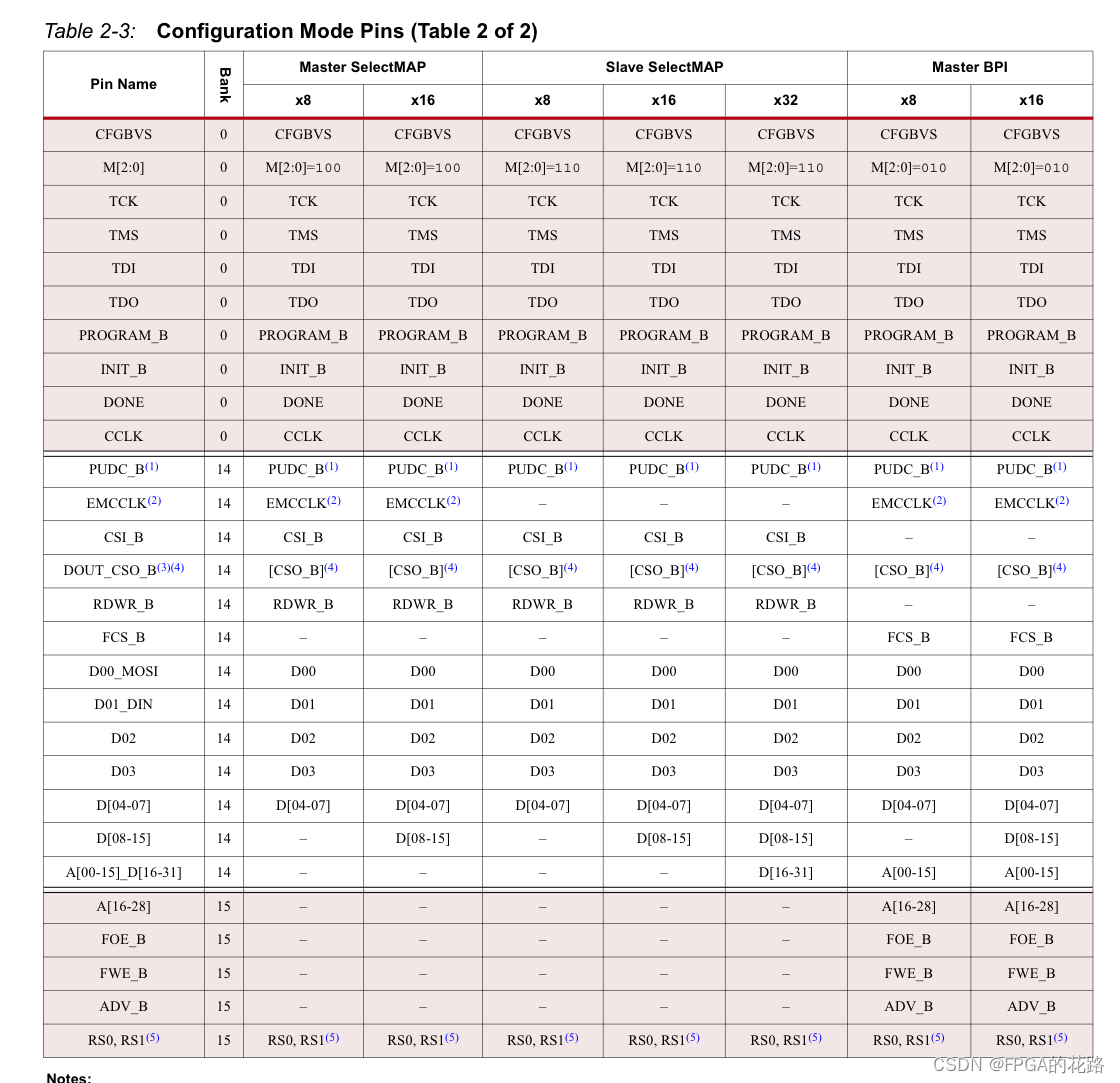

- й…ҚзҪ®еј•и„ҡ

- CVGBVS

- PROGRAM_B

- INIT_B

- PUDC_B

- VCCBATT

- RS0, RS1

- RDWR_B

- FCS_B

- FOE_B

- FWE_B

- Configuration Details

- й…ҚзҪ®ж–Үд»¶ж јејҸ

- жҖ»зәҝдҪҚе®ҪиҮӘеҠЁжЈҖжөӢ

- еҗҢжӯҘеӯ—

- дҪҚдәӨжҚўе’ҢжҖ»зәҝеӯ—еәҸ

- 延иҝҹй…ҚзҪ®

- 延иҝҹзӣёе…ідҝЎеҸ·

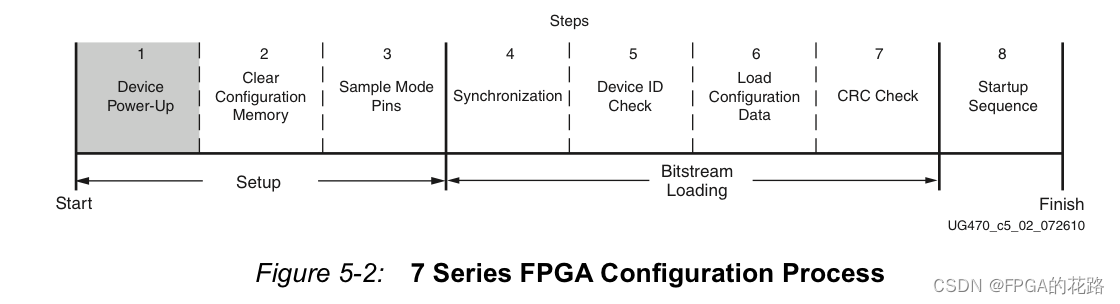

- й…ҚзҪ®йЎәеәҸ

- Setup

- Device Power-Up (Step 1)

- Clear Configuration Memory (Step 2, Initialization)

- Sample Mode Pins (Step 3)

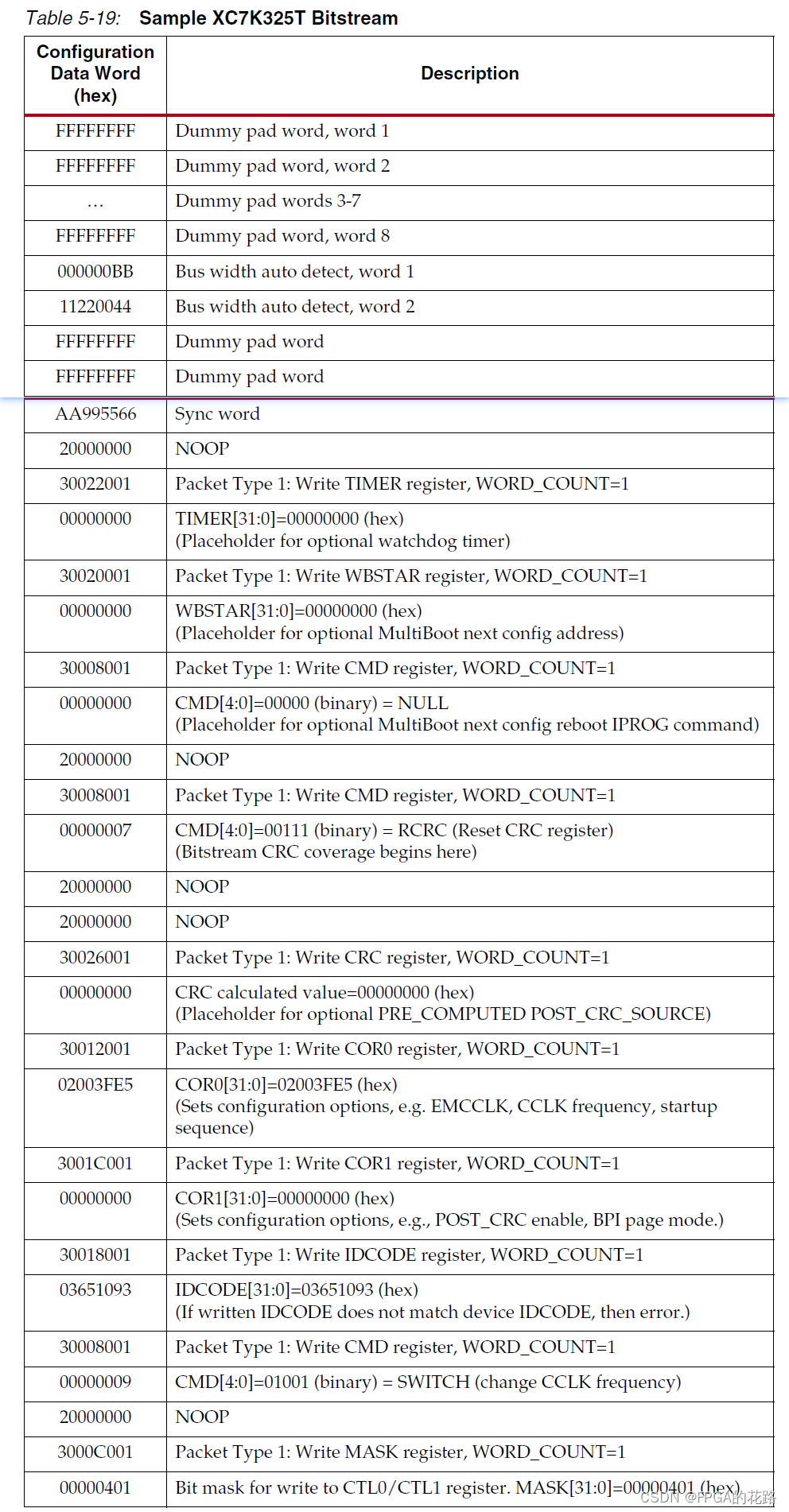

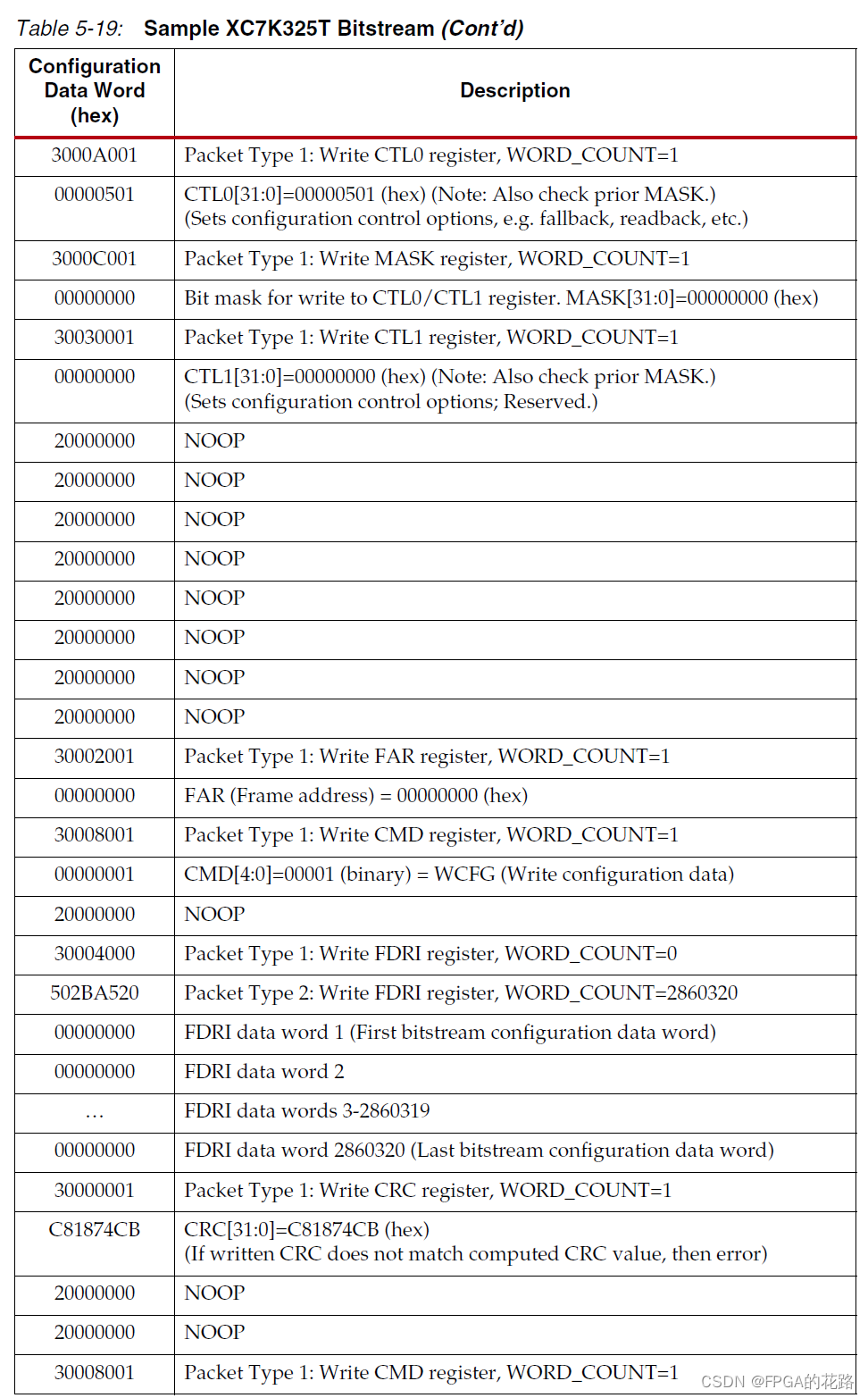

- Bitstream Loading

- Synchronization (Step 4)

- Check Device ID (Step 5)

- Load Configuration Data Frames (Step 6)

- Cyclic Redundancy Check (Step 7)

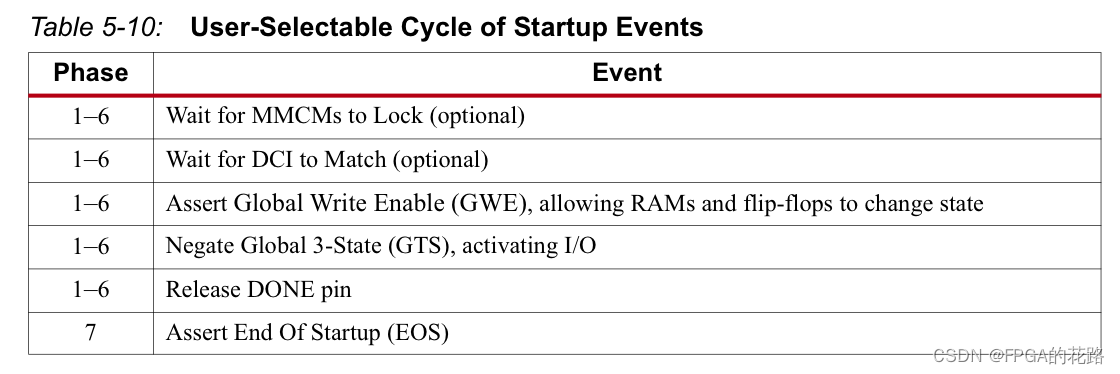

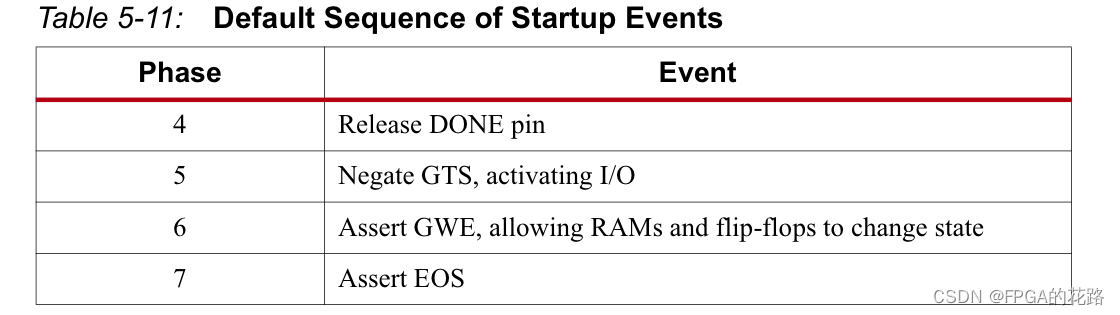

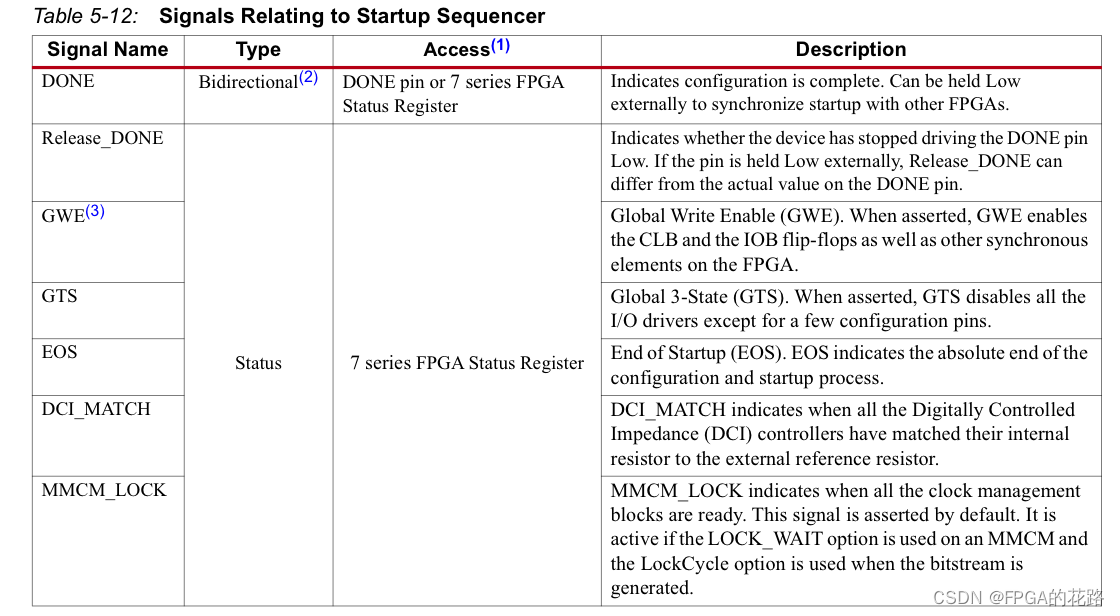

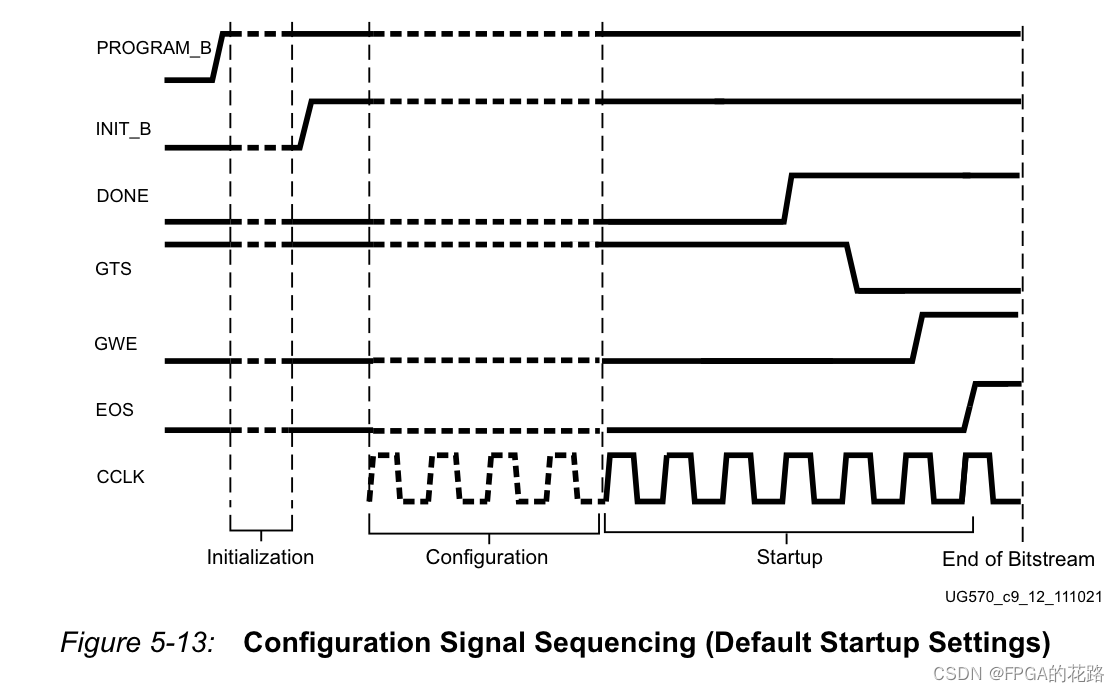

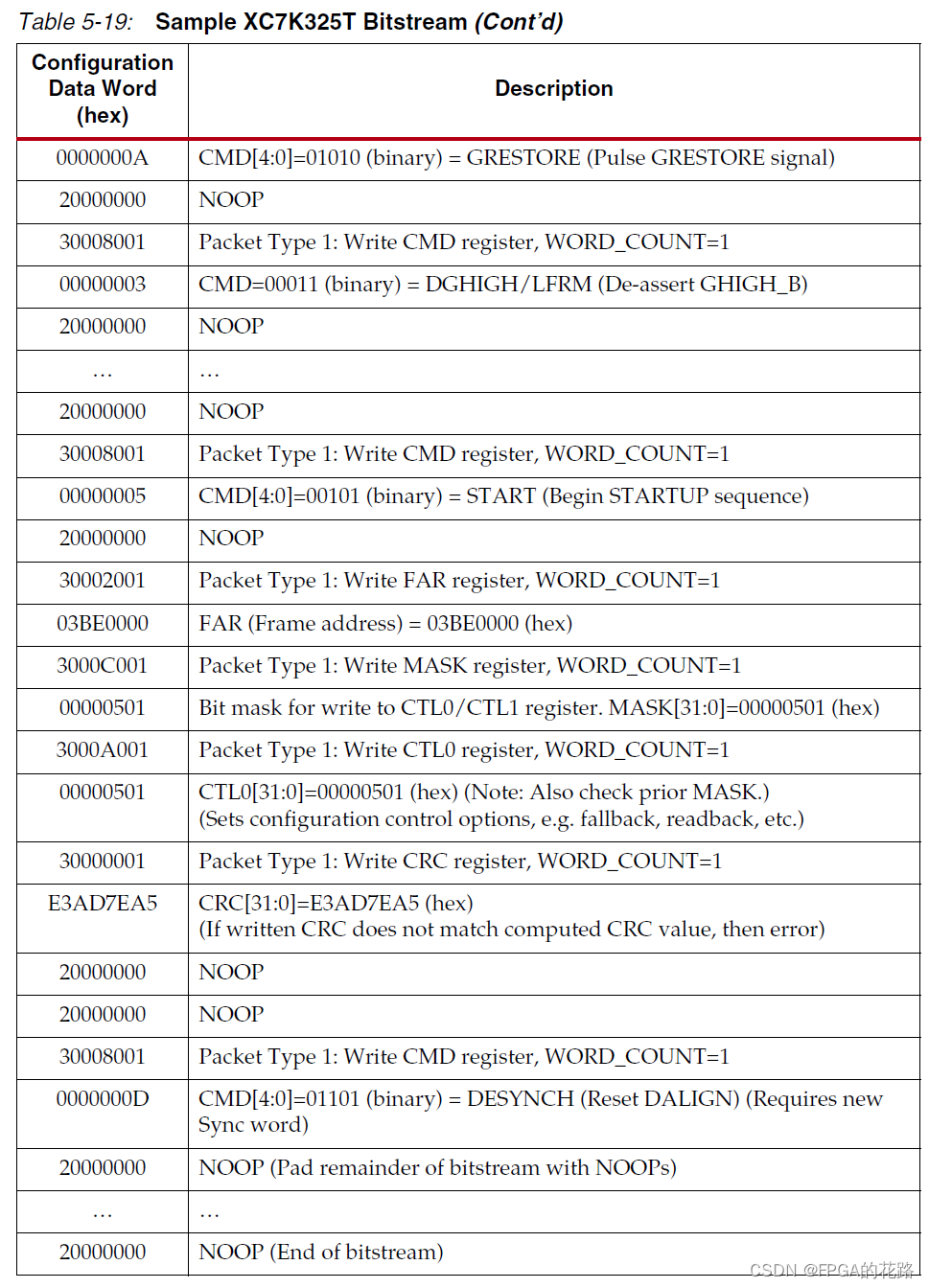

- Startup

- й…ҚзҪ®иҝҮзЁӢI/Oз”өе№іеҸҳеҢ–пјҲEOSпјү

- STARTUPE2еҺҹиҜӯ

- Bitstream Security

- Bitstream Composition

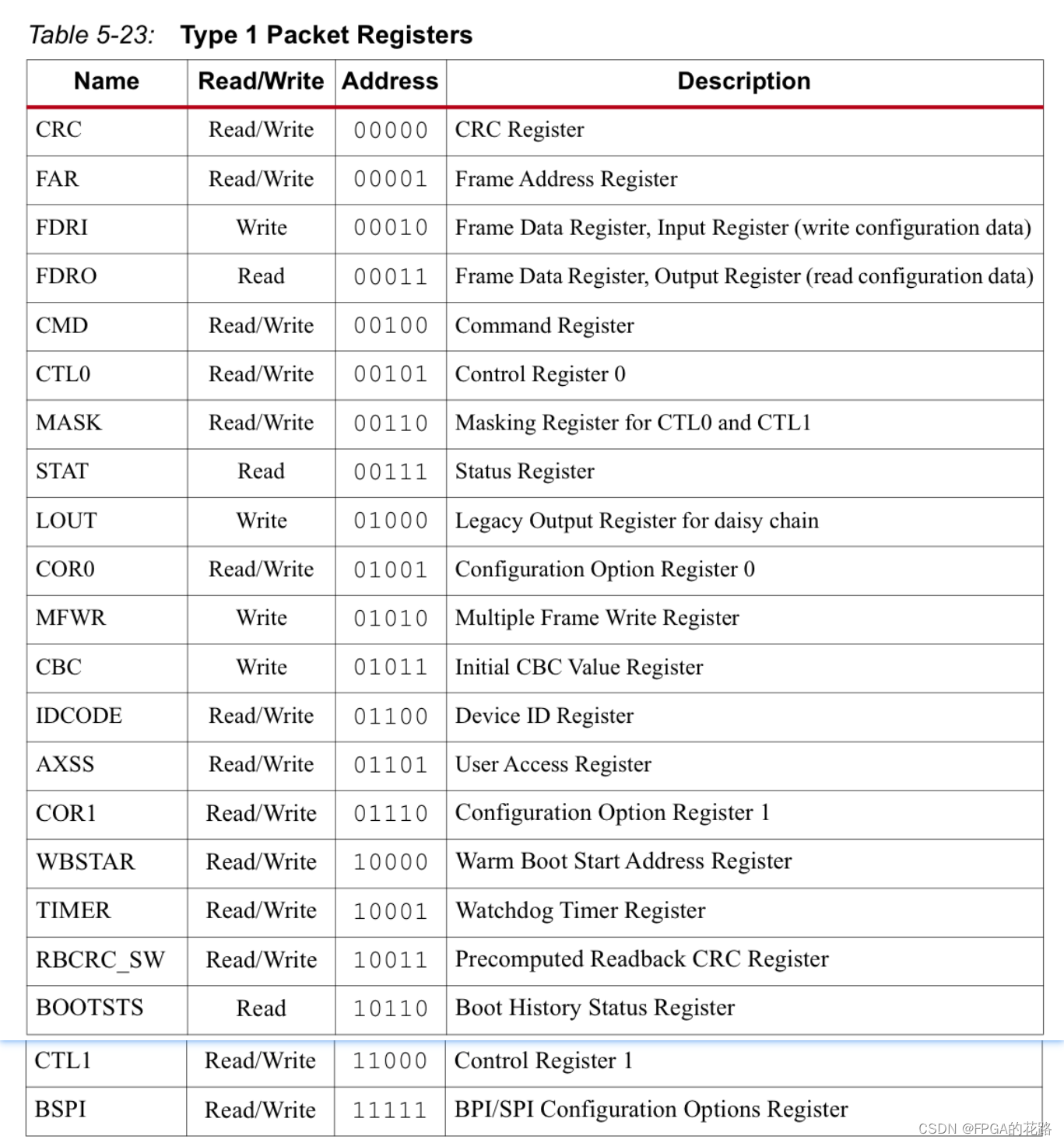

- й…ҚзҪ®еҜ„еӯҳеҷЁ

- йҮҚй…ҚзҪ®е’ҢеӨҡй•ңеғҸ

- Fallback MultiBoot

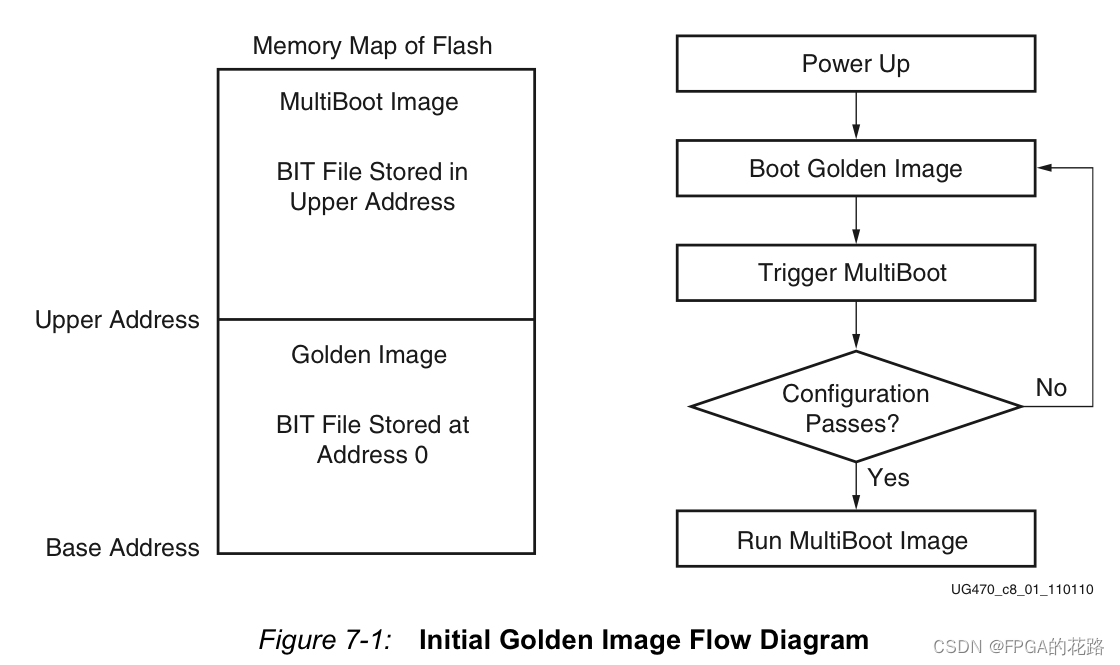

- е…ҲеҠ иҪҪgoldenеҶҚи§ҰеҸ‘MultiBoot

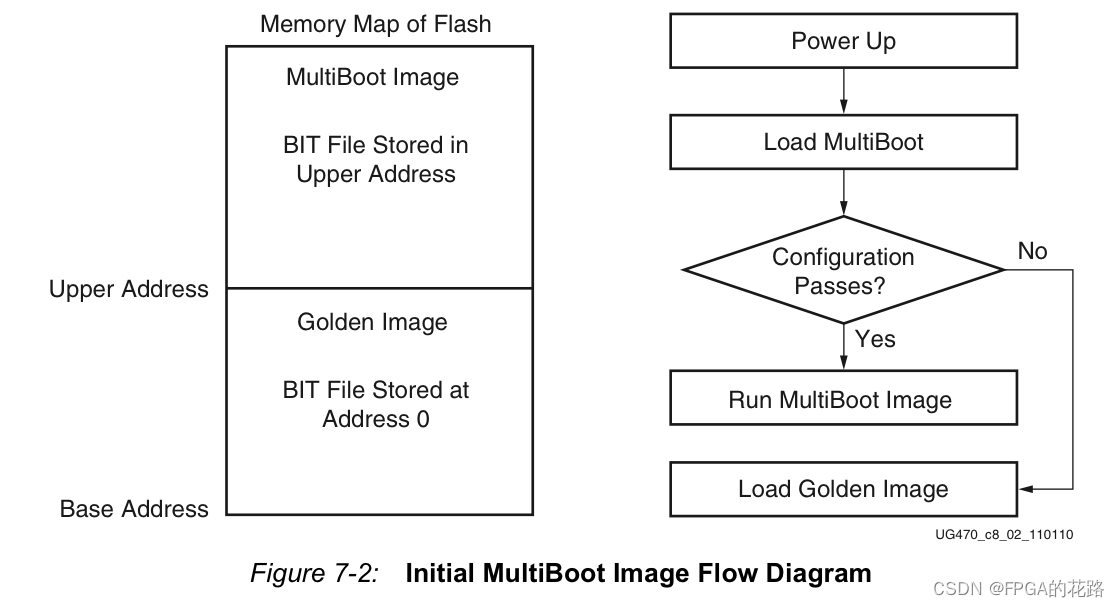

- зӣҙжҺҘеҠ иҪҪMultiBoot

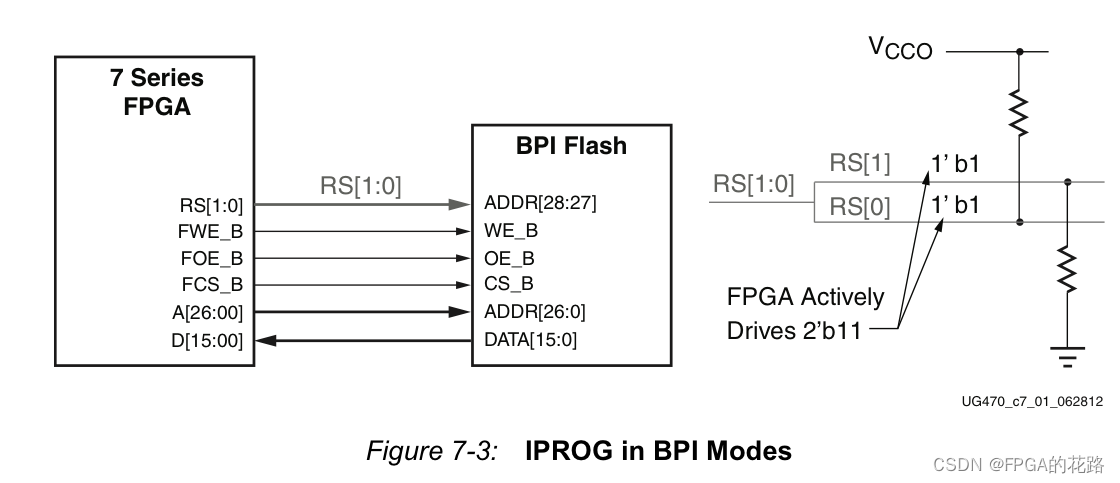

- IPROG

- IPROG Using ICAPE2

- IPROG Embedded in the Bitstream

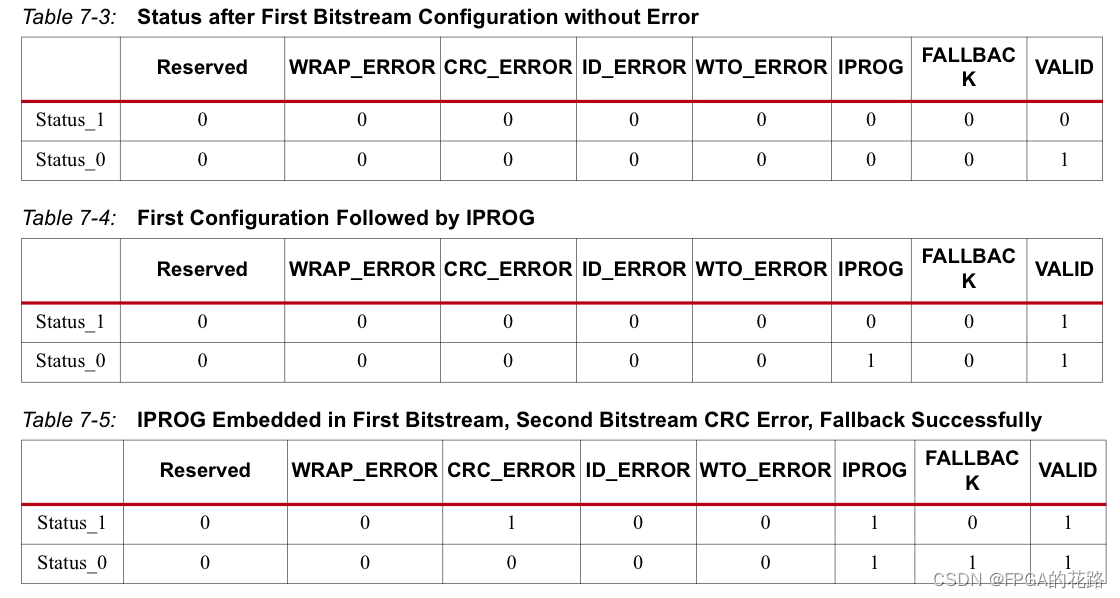

- Status Register for Fallback and IPROG Reconfiguration

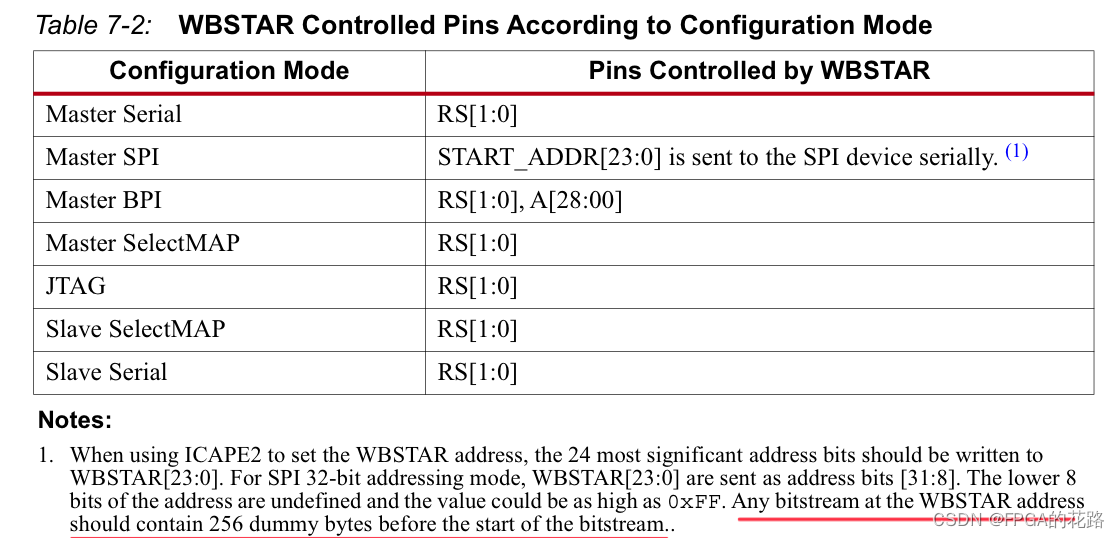

- WBSTAR Register

- Watchdog Timer

- Configuration Monitor Mode

- User Monitor Mode

- RS Pins

- JTAGй«ҳзә§з”Ёжі•

- еҸӮиҖғж–ҮзҢ®

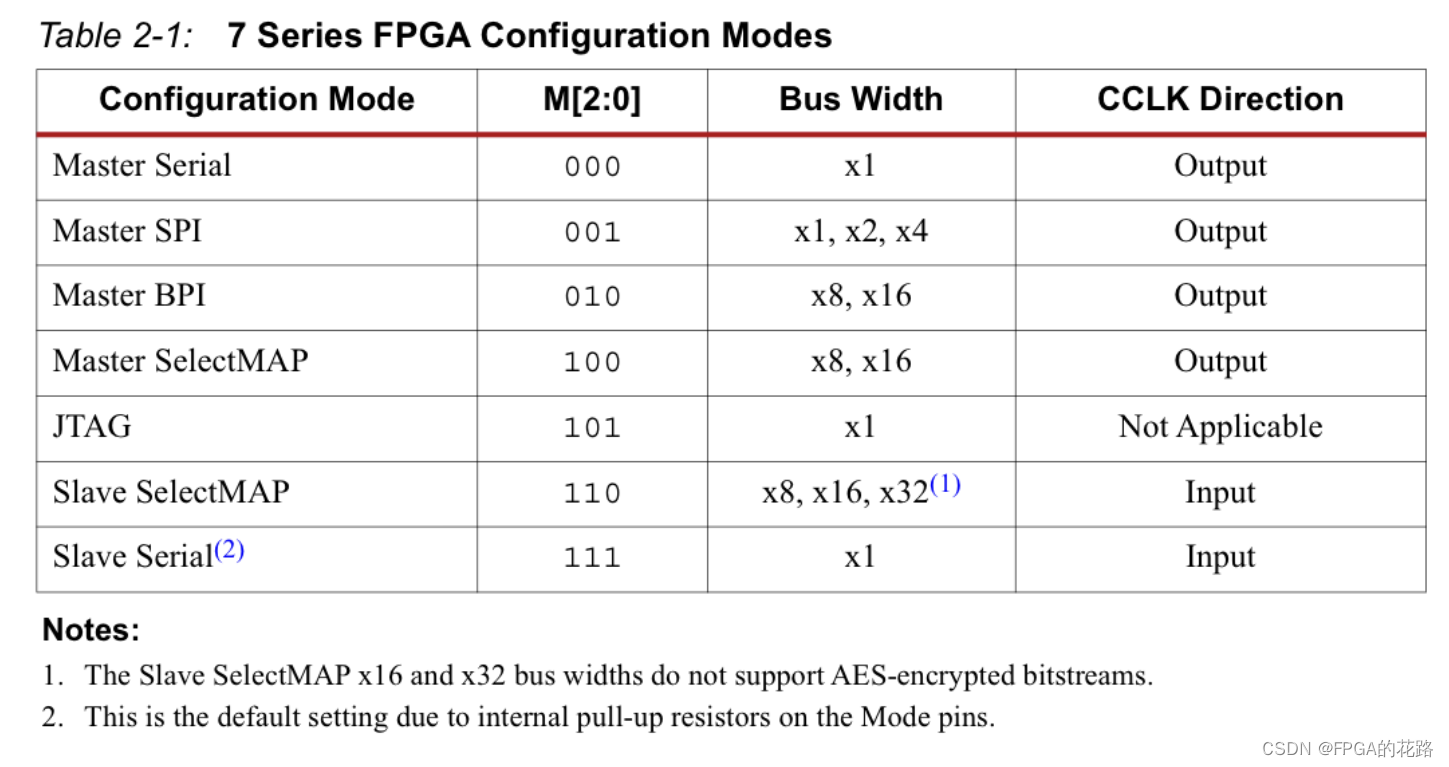

й…ҚзҪ®жЁЎејҸ

еҰӮжһң M[2:0] дёә вҖқ101вҖңпјҢеҲҷиҜҘFPGA еҸӘж”ҜжҢҒ JTAG иҝӣиЎҢй…ҚзҪ®гҖӮеӨ„дәҺе…¶дҪҷй…ҚзҪ®жЁЎејҸдёӢж—¶пјҢдҫқж—§еҸҜд»ҘдҪҝз”Ё JTAG жЁЎејҸиҝӣиЎҢи°ғиҜ•пјҢ并且дјҳе…Ҳзә§жңҖй«ҳгҖӮ

дёІиЎҢй…ҚзҪ®жЁЎејҸ

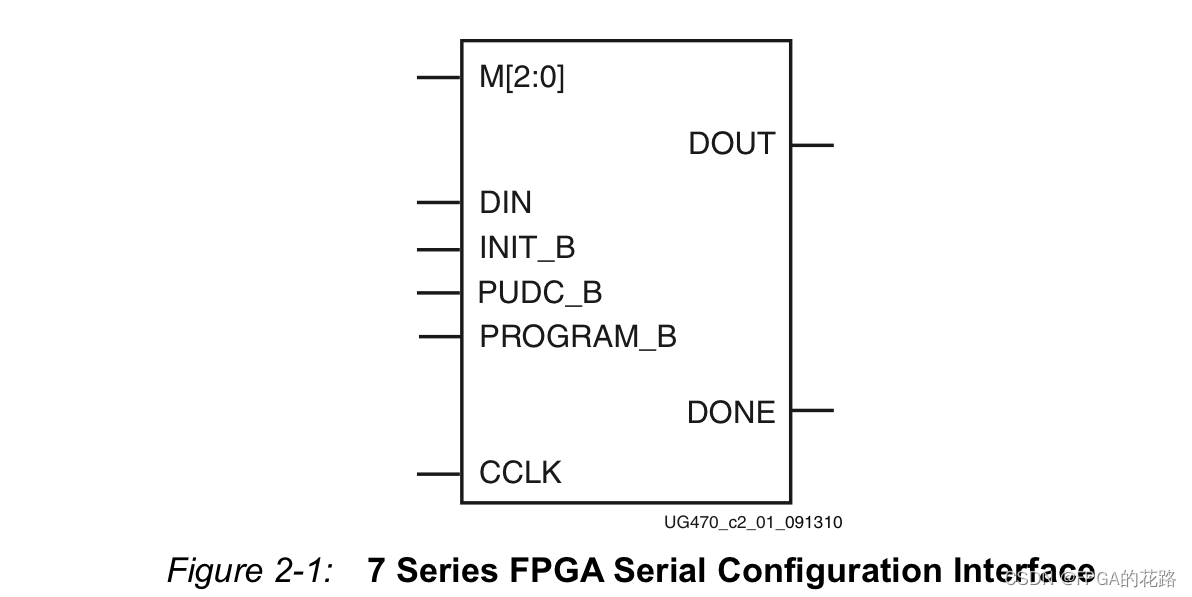

жҺҘеҸЈ

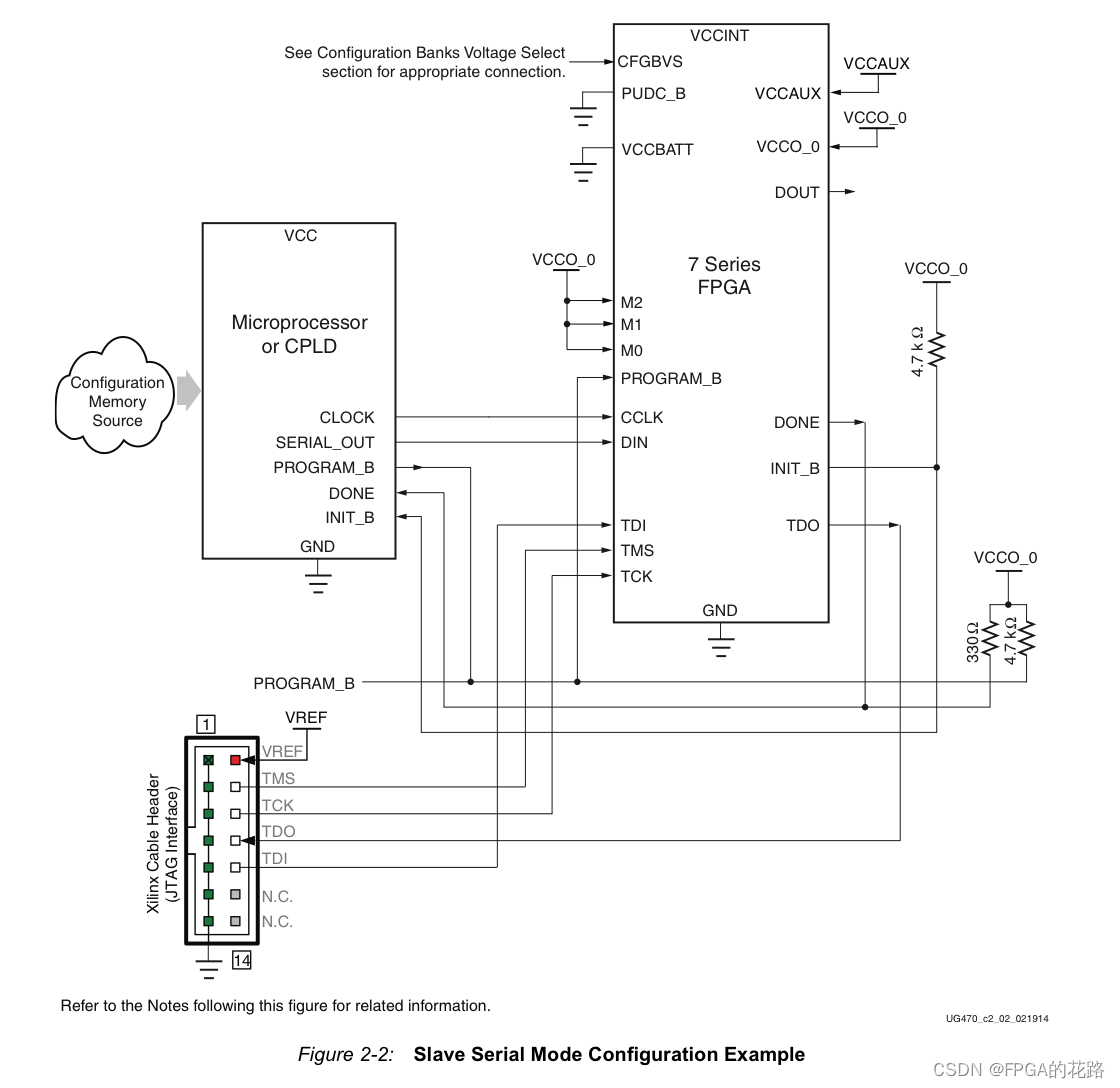

д»Һ-иҝһжҺҘж–№ејҸ

дё»-иҝһжҺҘж–№ејҸ

- йҷӨдәҶCCLK иҝһжҺҘдёҚеҗҢпјҢе…¶д»–йғҪе’Ңд»ҺдёІиЎҢжЁЎејҸдёҖж ·

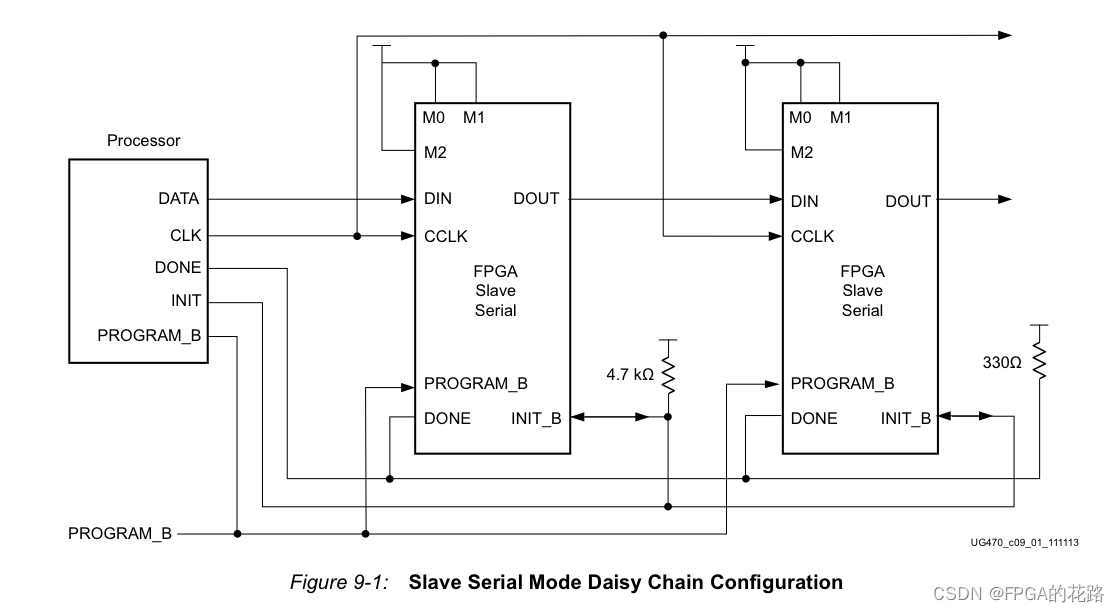

дёІиЎҢиҸҠиҠұй“ҫпјҲйқһеҗҢж—¶й…ҚзҪ®пјү

- дёҠеҚҮжІҝйҮҮж ·DINж•°жҚ®пјҢдёӢйҷҚжІҝDOUTиҫ“еҮәж•°жҚ®пјҢеҪўжҲҗдёҠдёӢжөҒе…ізі»пјӣ

- SPI еңЁиҜҘиҝһжҺҘж–№ејҸдёӢдёҚж”ҜжҢҒйҮҚй…ҚзҪ®еҠҹиғҪпјӣ

- 第дёҖдёӘеҷЁд»¶жңҖеҗҺе®ҢжҲҗй…ҚзҪ®пјӣеҪ“й“ҫдёӯжңҖиҝңз«ҜеҷЁд»¶е®ҢжҲҗй…ҚзҪ®пјҢеҲҷе°ҶDONEеҸҳдёәй«ҳйҳ»жҖҒпјҢиҝҷж ·дёӢдёҖдёӘеҷЁд»¶жЈҖжөӢеҲ°DONEдёәй«ҳеҲҷејҖе§Ӣй…ҚзҪ®пјӣ

- 7зі»еҲ—еҝ…йЎ»ж”ҫеңЁз¬¬дёҖдёӘпјӣ

- DOUTдј иҫ“зҡ„жҖ»ж•°жҚ®йҮҸжңүйҷҗеҲ¶пјҢжүҖд»ҘиҰҒж №жҚ®зЁӢеәҸеӨ§е°Ҹи®Ўз®—еҘҪеҸҜд»ҘиҝһжҺҘзҡ„еҷЁд»¶дёӘж•°

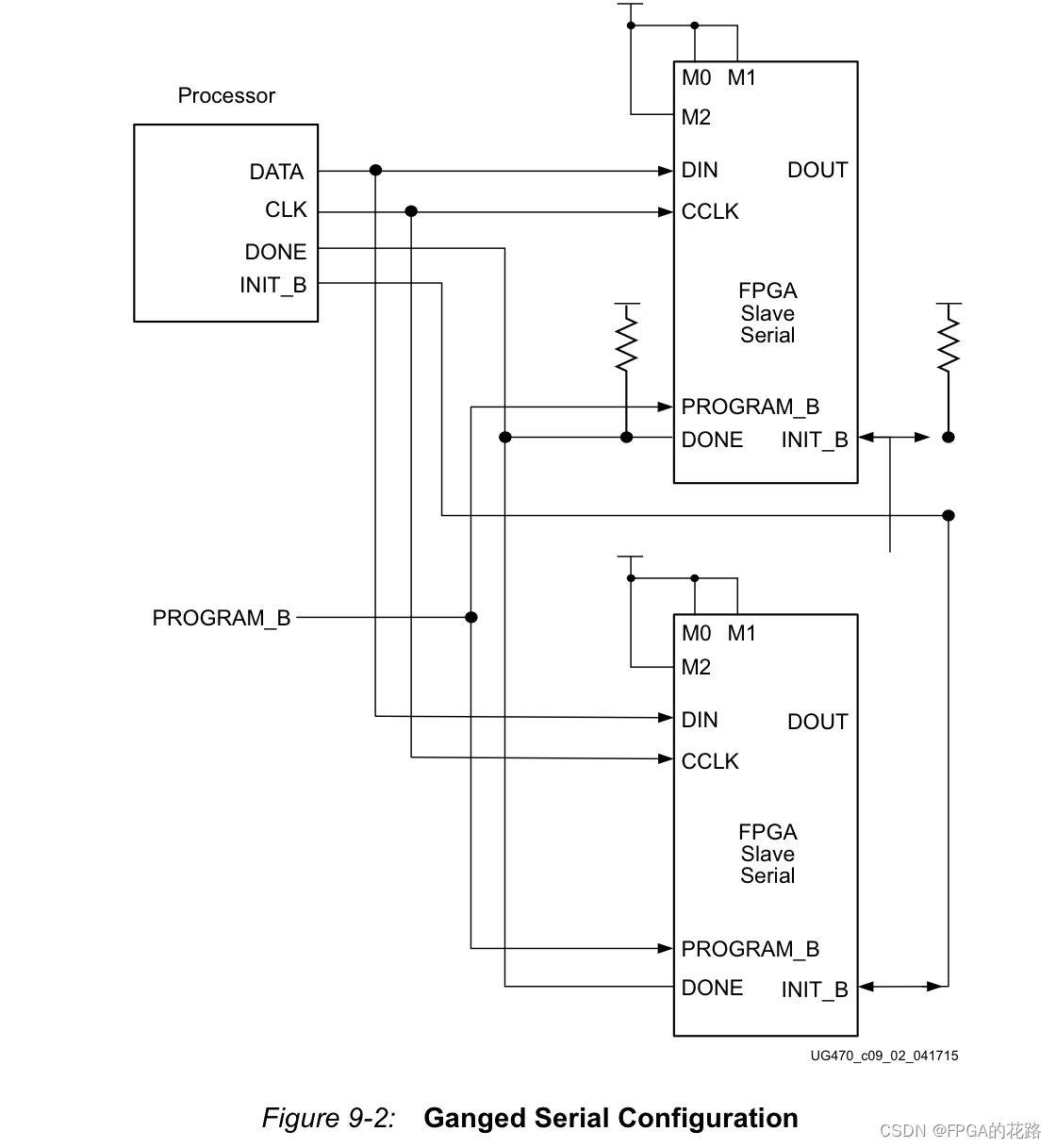

дёІиЎҢй…ҚзҪ®пјҲеҗҢж—¶й…ҚзҪ®пјү

- жүҖжңүеҷЁд»¶иҰҒдёҖж ·пјҲIDCODEдёҖж ·пјүпјҢй…ҚзҪ®зЁӢеәҸд№ҹдёҖж ·

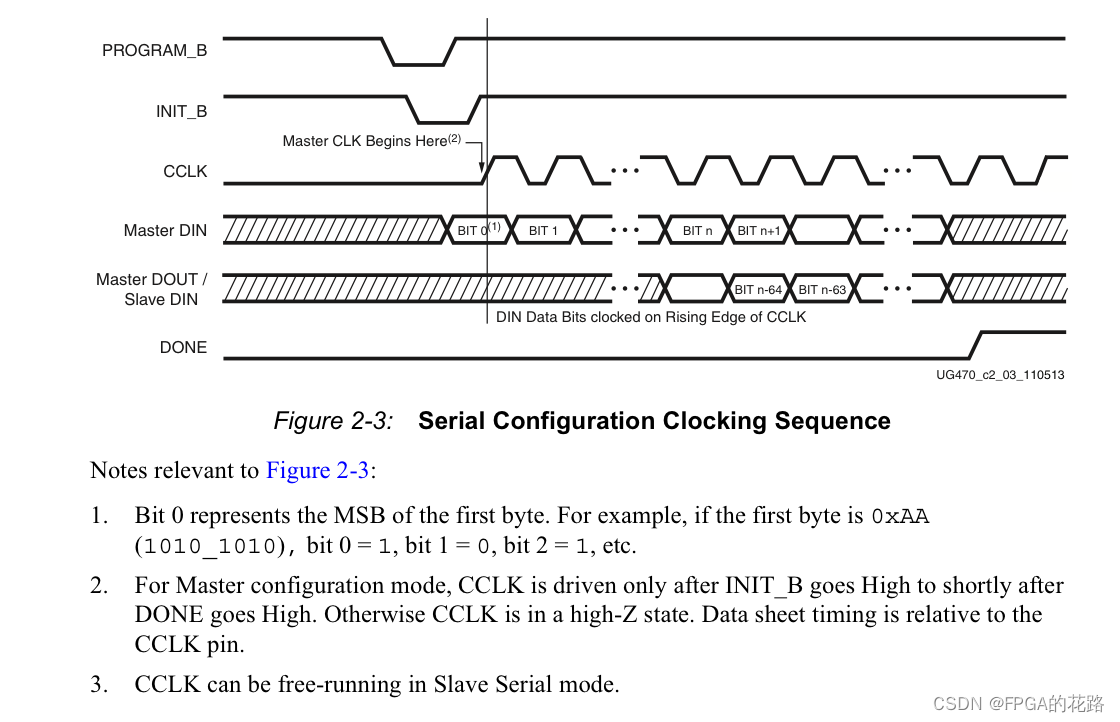

ж—¶еәҸ

дё»SPIй…ҚзҪ®жЁЎејҸ

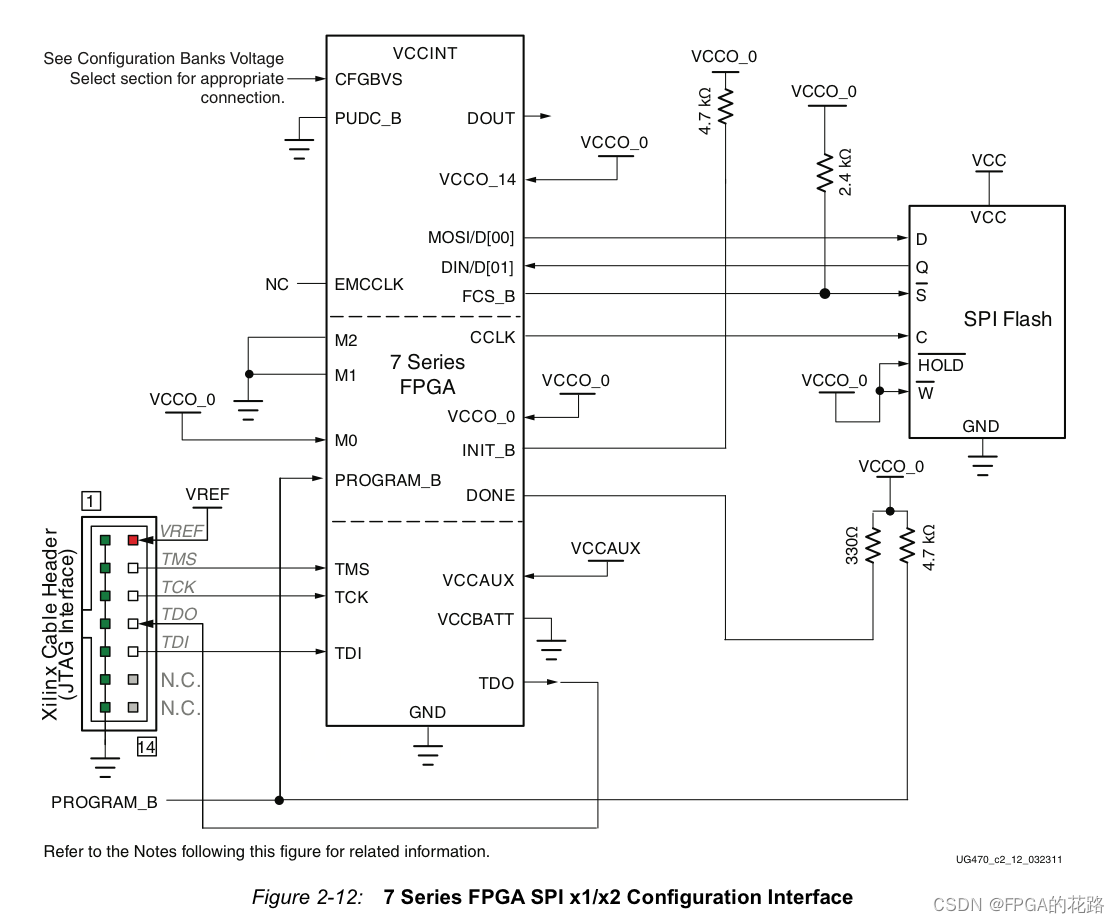

SPIx1/x2 иҝһжҺҘеӣҫ

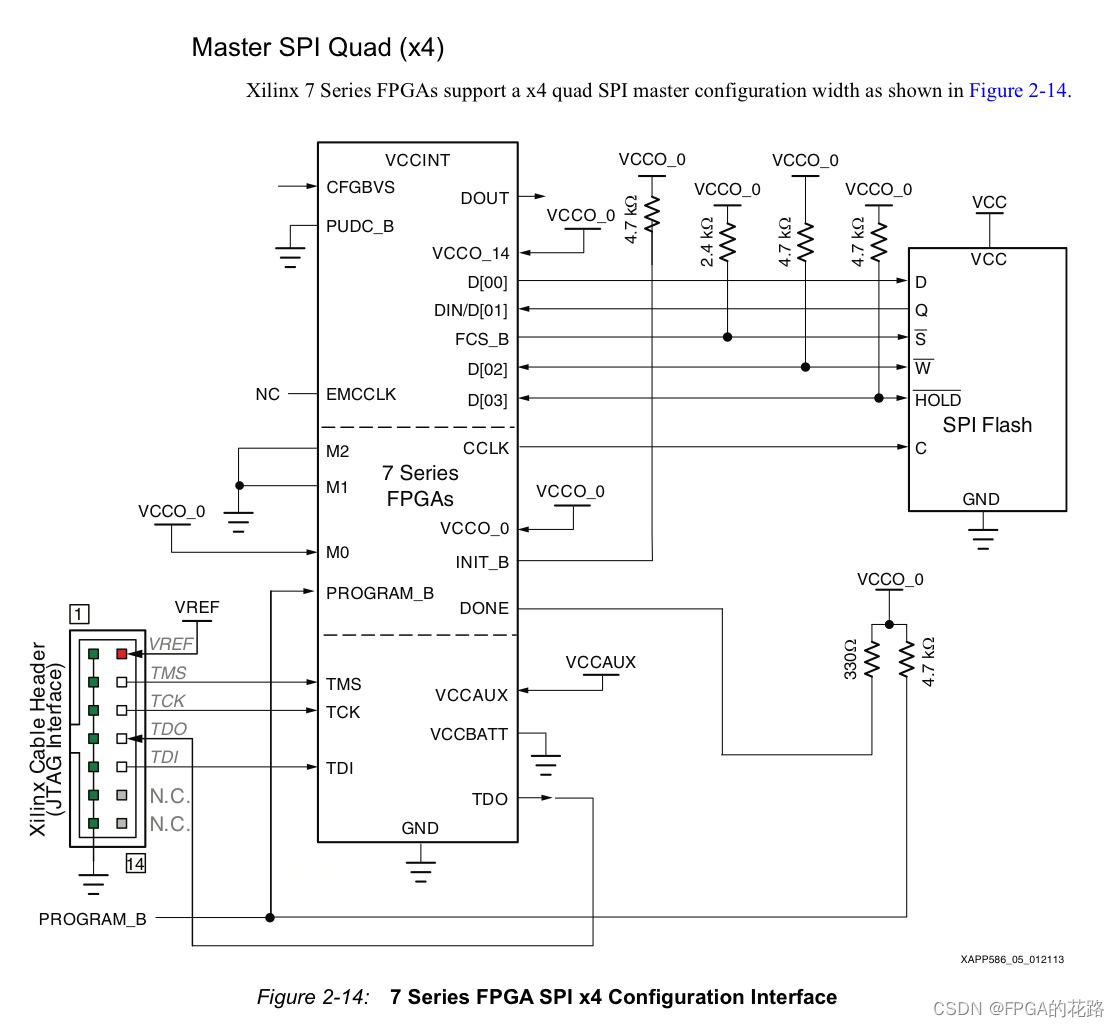

- INIT_B йңҖиҰҒеӨ–йғЁдёҠжӢүз”өйҳ»пјӣ

- иҸҠиҠұй“ҫжЁЎејҸдёҚж”ҜжҢҒSPIx2е’Ңx4пјҢDOUTиҝһжҺҘдёӢдёӘеҷЁд»¶зҡ„DINеҪўжҲҗиҸҠиҠұй“ҫпјӣ

- FPGA VCCO_0 иҰҒйҖӮй…Қ FLASHеҷЁд»¶зҡ„VCCпјӣ

- й»ҳи®ӨSPIеҷЁд»¶еңЁCCLKдёӢйҷҚжІҝй”Ғеӯҳж•°жҚ®пјҢFPGAеңЁдёҠеҚҮжІҝйҮҮж ·ж•°жҚ®пјҲеҸҜд»ҘйҖҡиҝҮй…ҚзҪ®SPI_FALL_EDGEеұһжҖ§жӣҙж”№дёәдёӢйҷҚжІҝйҮҮж ·пјүпјӣ

- еҸҜйҖҡиҝҮConfigRateеұһжҖ§и°ғиҠӮCCLKйў‘зҺҮпјӣеҸҜйҖҡиҝҮExtMasterCclk_enеұһжҖ§дҪҝиғҪеӨ–йғЁиҫ“е…Ҙж—¶й’ҹEMCCLKдҪңдёәCCLKжәҗдҪҝз”Ёпјӣ

- VCCBATTз”ЁдәҺAESеҜҶй’ҘеӯҳеӮЁпјҢйңҖиҰҒж—¶иҝһжҺҘ

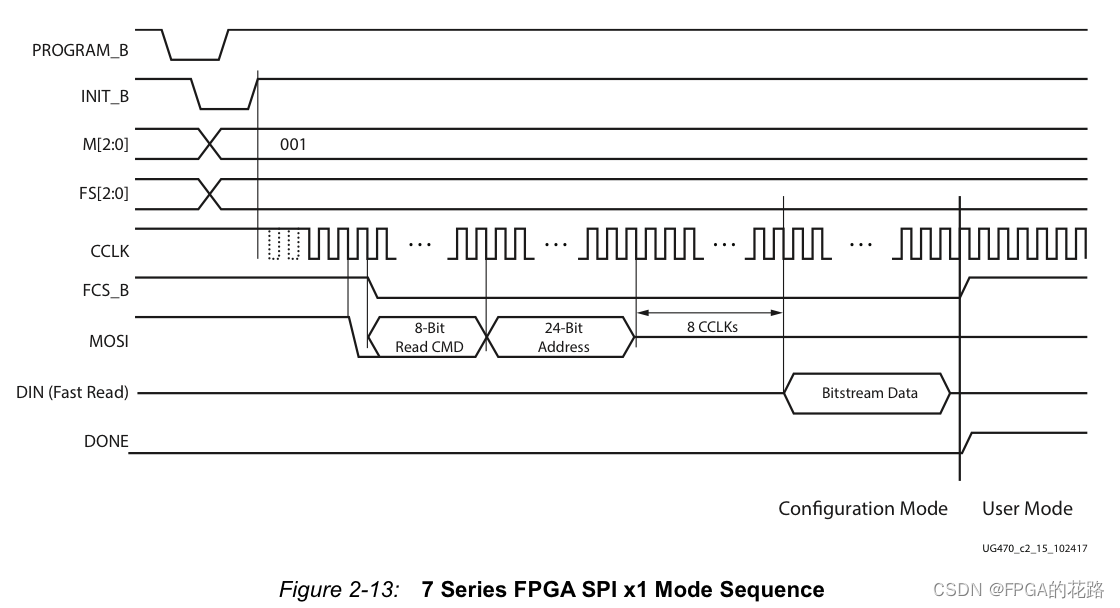

SPIx1жЁЎејҸж—¶еәҸ

- CCLKеҲқе§Ӣе§Ӣз»Ҳдёә3MHzпјҢй…ҚзҪ®ConfigRateеҸӘжңүеңЁиҜ»еҶҷж•°жҚ®ж—¶з”ҹж•ҲпјҢеҶҷең°еқҖе’ҢжҢҮд»Өж—¶дёҚз”ҹж•Ҳпјӣ

- SPI FLASHеңЁй…ҚзҪ®еҗҺдёҚдҪҝз”ЁпјҢе»әи®®е°ҶFCS_BжӢүй«ҳпјӣ

- PUDC_BдёәдҪҺпјҢеңЁеҶҷе®ҢиҜ»жҢҮд»Өе’Ңең°еқҖеҗҺпјҢMOSIйңҖиҰҒжӢүй«ҳжҲ–иҖ…дёәй«ҳйҳ»жҖҒ

SPIx4 иҝһжҺҘеӣҫ

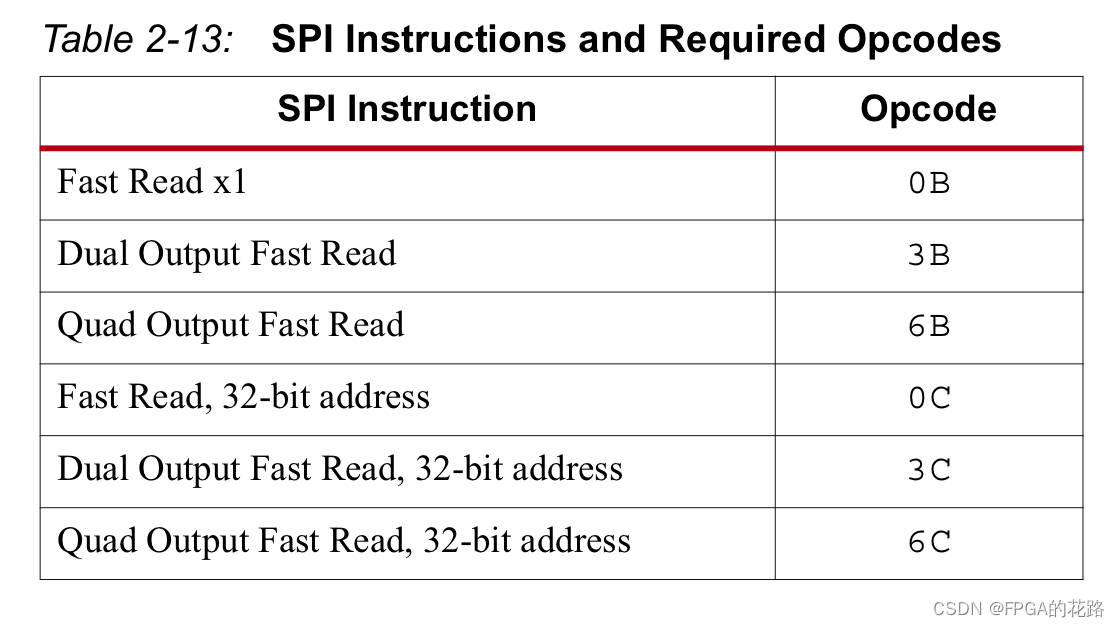

SPIж“ҚдҪңжҢҮд»Ө

- йҖҡиҝҮspi_buswidthеұһжҖ§ж”№еҸҳиҜ»еҶҷдҪҚе®Ҫ

ж“ҚдҪңflashз©әй—ҙеӨ§дәҺ128Mb

- йҖҡиҝҮдҪҝиғҪ spi_32bit_addr еұһжҖ§ж”ҜжҢҒ32bitең°еқҖжЁЎејҸ

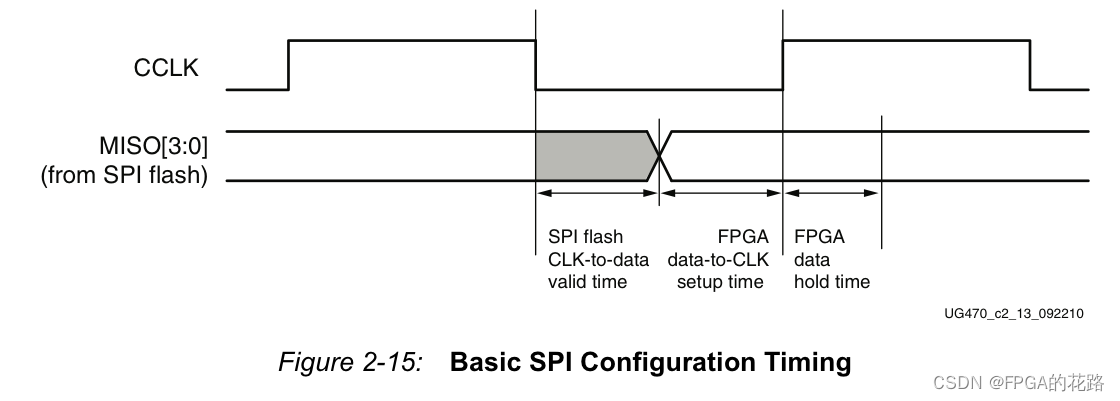

SPIй…ҚзҪ®ж—¶еәҸ

- й»ҳи®ӨSPIеҷЁд»¶еңЁCCLKдёӢйҷҚжІҝй”Ғеӯҳж•°жҚ®пјҢFPGAеңЁдёҠеҚҮжІҝйҮҮж ·ж•°жҚ®пјӣ

- еҸҜд»ҘйҖҡиҝҮй…ҚзҪ®SPI_FALL_EDGEеұһжҖ§жӣҙж”№дёәдёӢйҷҚжІҝйҮҮж ·пјҢдҪҶжҳҜдёҖејҖе§ӢиҝҳжҳҜдёҠеҚҮжІҝйҮҮж ·пјҢеҸӘжңүеҲ°иҜ»еҸ–bitжөҒдёӯзҡ„жӣҙж”№дёәдёӢйҷҚжІҝиҝҷдёӘй…ҚзҪ®дҝЎжҒҜд№ӢеҗҺжүҚдјҡз”ҹж•ҲпјҢиҝҷдёӘеңЁдҪҝиғҪеӨ–йғЁж—¶й’ҹжәҗе’Ңжӣҙж”№йҖҹзҺҮд№ӢеүҚз”ҹж•Ҳ

SPIжңҖеӨ§йҖҹзҺҮи®Ўз®—

дёҠз”өйЎәеәҸиҰҒжұӮ

SPI flashеҝ…йЎ»еңЁFPGA жӢүдҪҺFCS_Bе’ҢеҸ‘йҖҒиҜ»жҢҮд»Өд№ӢеүҚе…·еӨҮжҺҘеҸ—жҢҮд»ӨзҠ¶жҖҒ

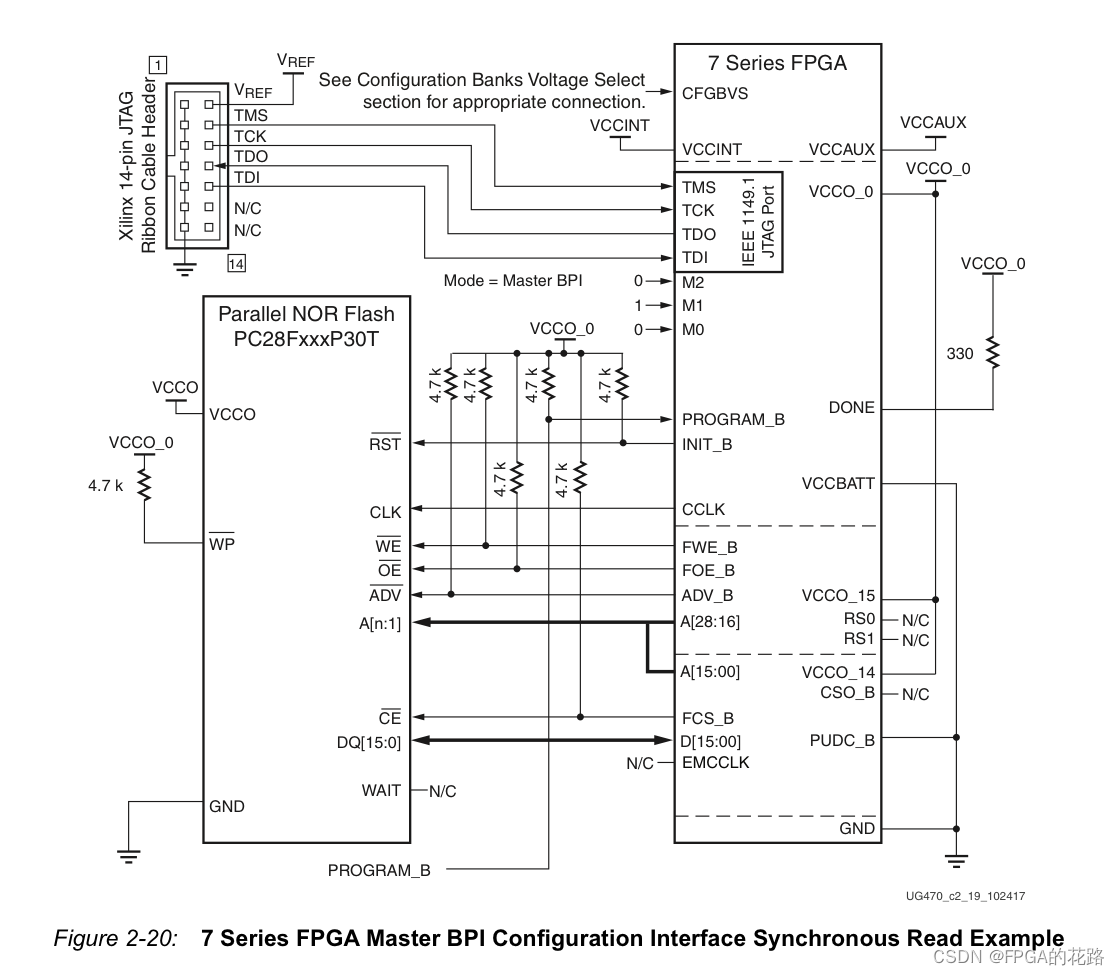

дё»BPIй…ҚзҪ®жЁЎејҸ

- жҹҗдәӣеј•и„ҡдҪҚдәҺ bank15пјҢArtix-7 дёӯ 7A50T д»ҘеҸҠжӣҙе°ҸеҷЁд»¶е’Ң Spartan-7зі»еҲ—дёҚж”ҜжҢҒ BPI й…ҚзҪ®пјӣ

- BPIжЁЎејҸж”ҜжҢҒејӮжӯҘе’ҢеҗҢжӯҘиҜ»еҸ–дёӨз§Қж–№ејҸпјҢй»ҳи®ӨејӮжӯҘпјӣ

- ејӮжӯҘиҜ»еҸ–ж”ҜжҢҒx8е’Ңx16дёӨз§ҚдҪҚе®ҪпјҢеқҮдёәиҮӘеҠЁиҜҶеҲ«

жҺҘеҸЈ

ејӮжӯҘиҜ»еҸ–жЁЎејҸ

иҝһжҺҘеӣҫ

- BPIжЁЎејҸпјҡM[2:0]= 101 пјӣ

- CCLKеҝ…йЎ»дҪңдёәиҫ“еҮәжӮ¬з©әпјӣ

- RS[1:0]з”ЁдәҺеӨҡй•ңеғҸй…ҚзҪ®пјҲMultiBootпјү

ж—¶еәҸ

- ејҖе§Ӣй…ҚзҪ®пјҡдёҠз”өжҲ–иҖ…дҪҺи„үеҶІPROGRAM_BдҝЎеҸ·пјӣ

- дёҠз”өй…ҚзҪ®пјҡPROGRAM_BдҪҺз”өе№іж—¶жӢүдҪҺINIT_B;

- еҲқе§ӢеҢ–е®ҢжҲҗпјҡINIT_BеҸҳй«ҳпјҢINIT_BдёҠеҚҮжІҝйҮҮж ·M[2:0]пјҢиҜҶеҲ«й…ҚзҪ®жЁЎејҸпјӣ

- иҜҶеҲ«дёәBPIжЁЎејҸпјҡFWE_BжӢүй«ҳпјҢFOE_BжӢүдҪҺпјҢFCS_BжӢүдҪҺпјӣ

- дё»жЁЎејҸж—¶INIT_BдёҠеҚҮжІҝдёҖж®ө延时еҗҺиҫ“еҮәCCLKпјӣ

- FPGAиҫ“еҮәеҲқе§Ӣең°еқҖ并з»ҙжҢҒ10дёӘCCLKпјӣ

- FPGAеңЁCCLKдёҠеҚҮжІҝиҜ»еҸ–ж•°жҚ®пјӣ

- CRCй”ҷиҜҜпјҢINIT_Bиҫ“еҮәдҪҺпјҢDONEдҝқжҢҒдҪҺз”өе№іпјӣ

- еҠ иҪҪе®ҢжҲҗпјҢDONEжӢүй«ҳпјӣ

- CCLKеҸҳдёәй«ҳйҳ»жҖҒпјӣ

- еңЁGTS_cycleеҗҺеӨҡеҠҹиғҪI/Oеј•и„ҡеҸҳдёәз”ЁжҲ·жЁЎејҸпјҢй»ҳи®ӨдёәDONEеҸҳдёәй«ҳеҗҺдёҖдёӘе‘Ёжңҹ

еҗҢжӯҘиҜ»еҸ–жЁЎејҸ

иҝһжҺҘеӣҫ

- еҗҢжӯҘиҜ»еҸ–жЁЎејҸжҳҜжңҖеҝ«зҡ„й…ҚзҪ®жЁЎејҸпјӣ

- дёҖејҖе§ӢдҪҝз”Ёй»ҳи®ӨCCLKйҖҹзҺҮе’ҢејӮжӯҘиҜ»еҸ–жЁЎејҸпјҢзӣҙеҲ°иҜ»еҸ–bitstreamзҡ„headerжүҚиҪ¬жҚўдёәеҗҢжӯҘиҜ»жЁЎејҸпјӣ

- еҗҢжӯҘжЁЎејҸйңҖиҰҒйҖҡиҝҮи®ҫзҪ®BPI_sync_modeеұһжҖ§и®ҫзҪ®пјҢжңүдёӨз§ҚеұһжҖ§еҖјпјҡType1пјҲз”ЁдәҺG18FдҝЎеҸ·flashпјүпјӣType2пјҲз”ЁдәҺP30/P33дҝЎеҸ·flashпјүпјӣ

- еҗҢжӯҘиҜ»жЁЎејҸпјҢFPGA CCLKиҫ“еҮәиҝһжҺҘBPI FlashпјҢADV_BиҝһжҺҘFLASH ADVеј•и„ҡпјӣ

- FPGAй…ҚзҪ®е®ҢжҲҗеҗҺ BPI flashдҝқжҢҒеҗҢжӯҘиҜ»жЁЎејҸпјӣ

- еҗҢжӯҘиҜ»жЁЎејҸеҸӘж”ҜжҢҒx16пјӣ

- bitйЎәеәҸе’ҢSelectMapдёҖж ·

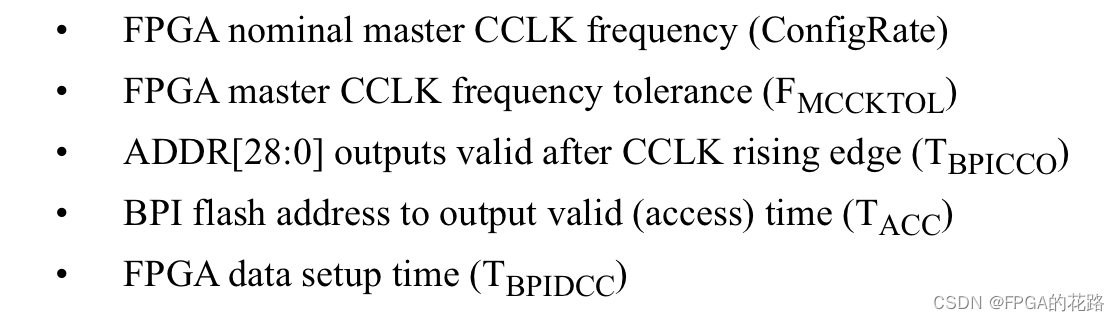

жңҖеӨ§й…ҚзҪ®йҖҹзҺҮи®Ўз®—

дёҠз”өйЎәеәҸиҰҒжұӮ

- еңЁFPGAй©ұеҠЁFCS_BдҪҺз”ө平并иҫ“еҮә第дёҖдёӘең°еқҖд№ӢеүҚпјҢBPIй—Әеӯҳеҝ…йЎ»еҮҶеӨҮеҘҪиҝӣиЎҢејӮжӯҘиҜ»еҸ–пјҢд»ҘзЎ®дҝқBPIй—ӘеӯҳеҸҜд»Ҙиҫ“еҮәеӯҳеӮЁзҡ„жҜ”зү№жөҒгҖӮ

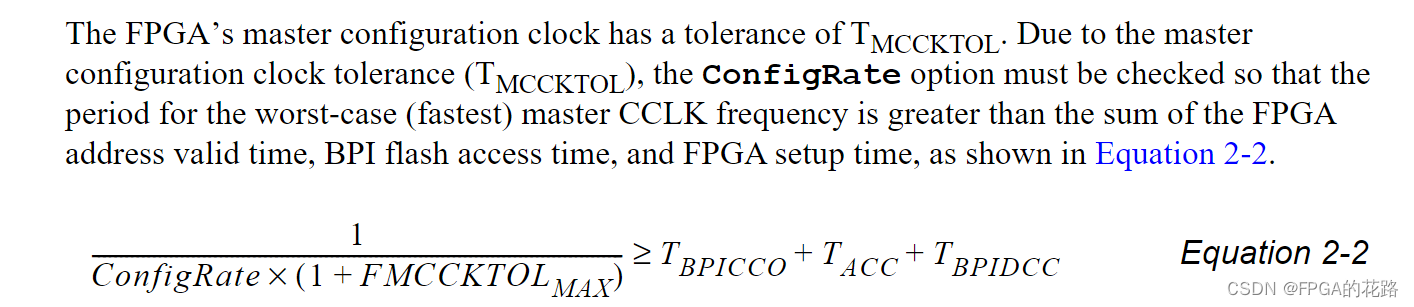

SelectMAP й…ҚзҪ®жЁЎејҸ

з®Җд»Ӣ

-

жҖ»зәҝе®ҪеәҰ 8гҖҒ16гҖҒ32bitsпјҢеҸҜд»ҘиҮӘеҠЁиҜҶеҲ«жҖ»зәҝе®ҪеәҰпјӣ

-

ж”ҜжҢҒй…ҚзҪ®е’ҢиҜ»еҸ–ж“ҚдҪңпјӣ

-

иҜ»ж“ҚдҪңеҸӘжңүд»Һ SelectMAPжЁЎејҸж”ҜжҢҒпјӣ

-

CCLKдё»жЁЎејҸдёӢдёәиҫ“еҮәпјӣд»ҺжЁЎејҸдёӢдёәиҫ“е…Ҙпјӣ

-

жЁЎејҸпјҡеҚ•еҷЁд»¶д»ҺжЁЎејҸгҖҒеӨҡеҷЁд»¶иҸҠиҠұй“ҫжЁЎејҸгҖҒеӨҡзӣёеҗҢеҷЁд»¶жЁЎејҸ

жҺҘеҸЈ

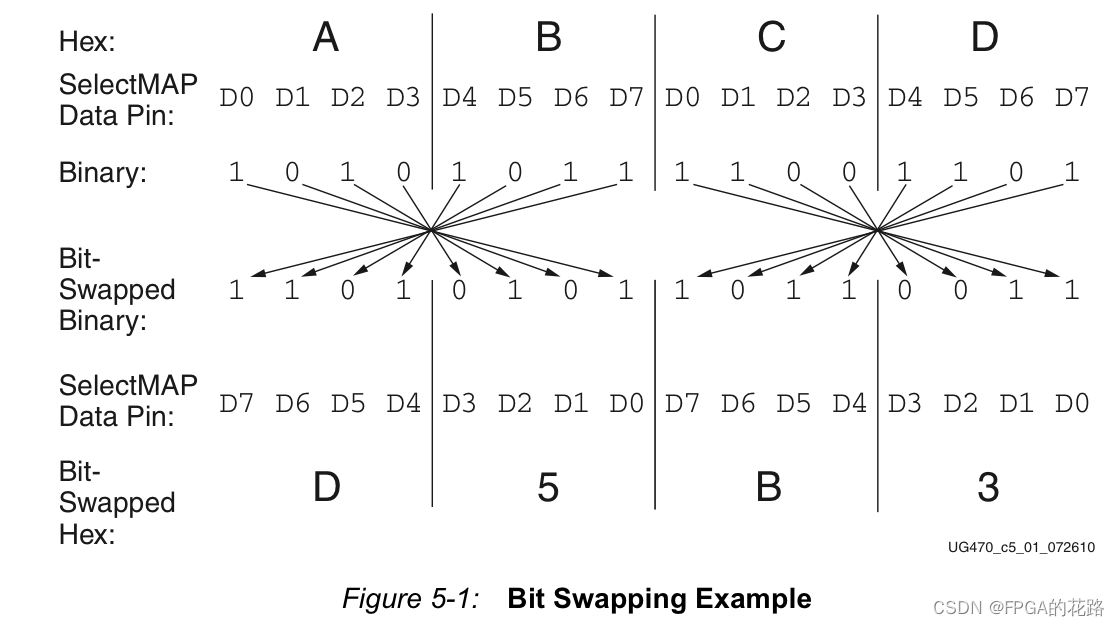

Data Ordering

еҚ•еҷЁд»¶й…ҚзҪ®жЁЎејҸ

иҝһжҺҘзӨәдҫӢ

ж•°жҚ®еҠ иҪҪ

ж”ҜжҢҒиҝһз»ӯе’Ңйқһиҝһз»ӯж•°жҚ®еҠ иҪҪпјҢж•°жҚ®еҠ иҪҪз”ұ CSI_BгҖҒRDWR_BгҖҒCCLKдҝЎеҸ·жҺ§еҲ¶

-

CSI_B

-

SelectMAP жҺҘеҸЈдҪҝиғҪпјҢдҪҺжңүж•Ҳпјӣ

-

еҪ“дёҚйңҖиҰҒSelectMAPе’ҢиҜ»еӣһж“ҚдҪңж—¶пјҢCSI_BеҸҜд»ҘжҺҘең°

-

RDWR_B

- иҫ“е…Ҙиҫ“еҮәдҪҝиғҪпјҢдҪҺз”өе№іиҫ“е…ҘпјҲеҶҷFPGA)пјҢй«ҳз”өе№іиҫ“еҮәпјҲиҜ»FPGA)пјӣ

- CSI_BдҪҝиғҪж—¶пјҢRDWR_BдҝқжҢҒдёҚеҸҳпјҢеҗҰеҲҷдјҡдёӯж–ӯй…ҚзҪ®е’ҢеӣһиҜ»ж“ҚдҪң

-

CCLK

- жүҖжңүж•°жҚ®ж“ҚдҪңеҗҢжӯҘдәҺCCLKпјӣ

- й…ҚзҪ®FPGAпјҡFPGAеңЁж—¶й’ҹдёҠеҚҮжІҝйҮҮж ·пјӣ

- еӣһиҜ»FPGAпјҡFPGAеңЁж—¶й’ҹдёҠеҚҮжІҝжӣҙж–°ж•°жҚ®

иҝһз»ӯй…ҚзҪ®ж—¶еәҸ

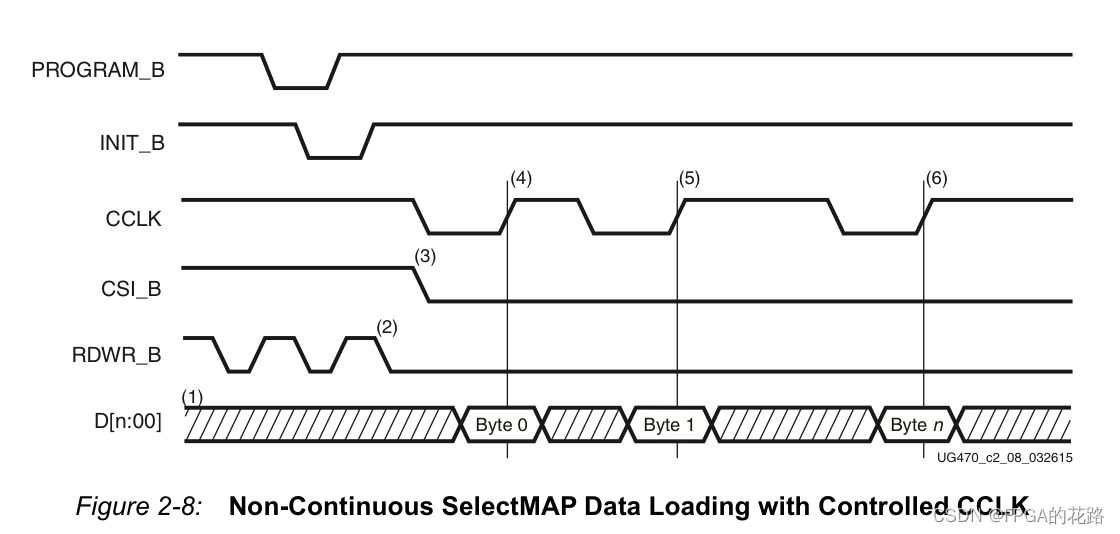

йқһиҝһз»ӯй…ҚзҪ®ж—¶еәҸ

дёӨз§Қйқһиҝһз»ӯй…ҚзҪ®ж–№ејҸпјҡ

- йҖҡиҝҮжҺ§еҲ¶CSI_BдҝЎеҸ·пјӣ

- йҖҡиҝҮжҺ§еҲ¶CCLKдҝЎеҸ·

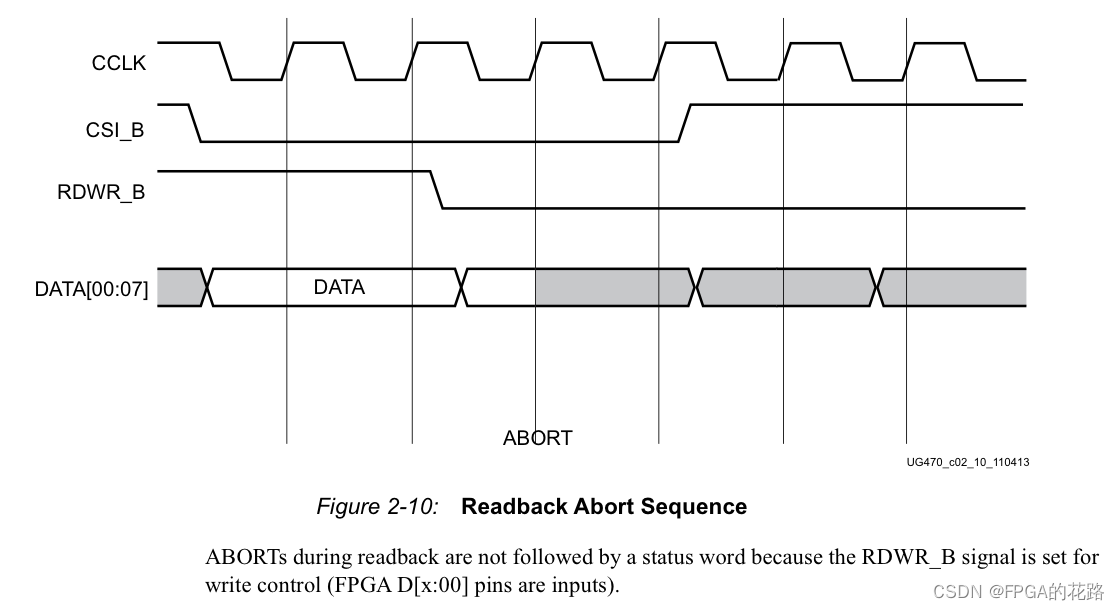

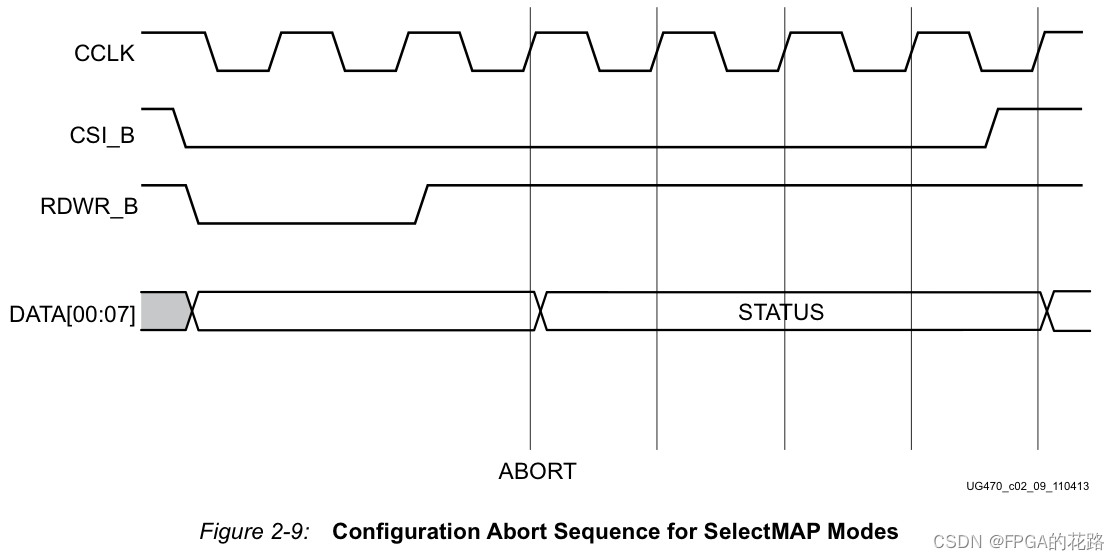

з»Ҳжӯўж“ҚдҪң

- еҲҶдёәй…ҚзҪ®з»Ҳжӯўе’ҢеӣһиҜ»з»Ҳжӯўж“ҚдҪңпјӣ

- еҪ“CSI_Bжңүж•Ҳж—¶ж”№еҸҳRDWR_Bи§ҰеҸ‘з»Ҳжӯўж“ҚдҪңпјӣ

- й…ҚзҪ®з»ҲжӯўдјҡжҢҒз»ӯ4дёӘCCLKе‘ЁжңҹпјҢеҗҢж—¶ж•°жҚ®зәҝD0-7дјҡиҝ”еӣһзҠ¶жҖҒеӯ—пјӣеӣһиҜ»з»ҲжӯўдёҚиҝ”еӣһзҠ¶еӯ—пјӣ

- з»Ҳжӯўж“ҚдҪңе®ҢжҲҗеҗҺдјҡжҒўеӨҚй…ҚзҪ®/еӣһиҜ»ж“ҚдҪңпјӣжҲ–иҖ…еҸҜд»ҘйҖҡиҝҮдә§з”ҹPROGRAM_BдҪҺи„үеҶІеӨҚдҪҚж•ҙдёӘеҷЁд»¶

ж—¶еәҸ

зҠ¶жҖҒеӯ—е®ҡд№ү

зҠ¶жҖҒеӯ—ж•°жҚ®еҜ№йҪҗ

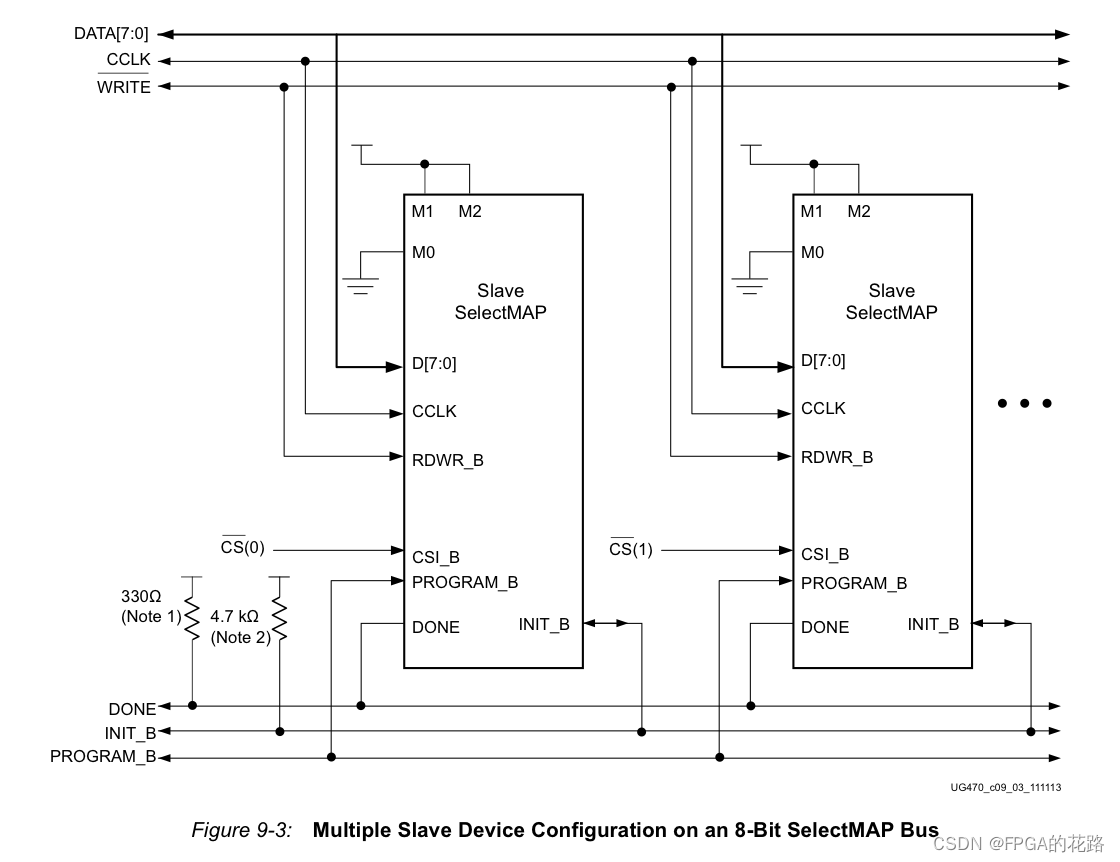

еӨҡеҷЁд»¶SelectMAPзӢ¬з«Ӣй…ҚзҪ®

- йҖҡиҝҮCSеҚ•зӢ¬жҺ§еҲ¶жҜҸдёӘеҷЁд»¶

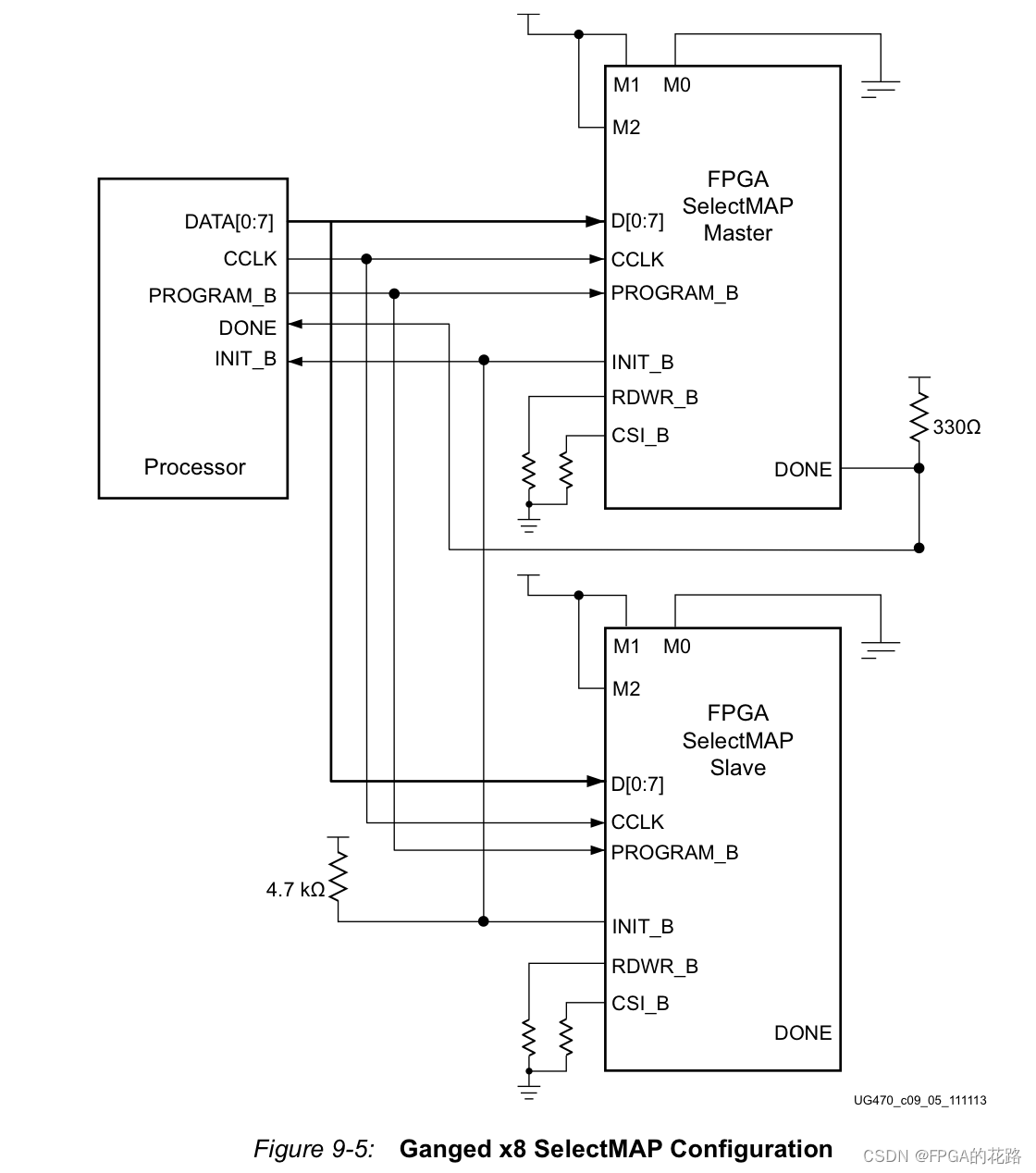

еӨҡеҷЁд»¶SelectMAPеҗҢж—¶й…ҚзҪ®

并иЎҢиҸҠиҠұй“ҫй…ҚзҪ®

- CS_BдёәиҸҠиҠұй“ҫпјӣ

- 第дёҖдёӘеҷЁд»¶еҸҜд»ҘдёәMaster/Slave SelecrMAPгҖҒBPIпјҢе…¶д»–еҝ…йЎ»йғҪдёәSlave SelecrMAP

JTAGй…ҚзҪ®жЁЎејҸ

- ж— и®әM[2:0]й…ҚзҪ®дёәдҪ•еҖјпјҢйғҪж”ҜжҢҒJTAGеңЁзәҝй…ҚзҪ®

й…ҚзҪ®еј•и„ҡ

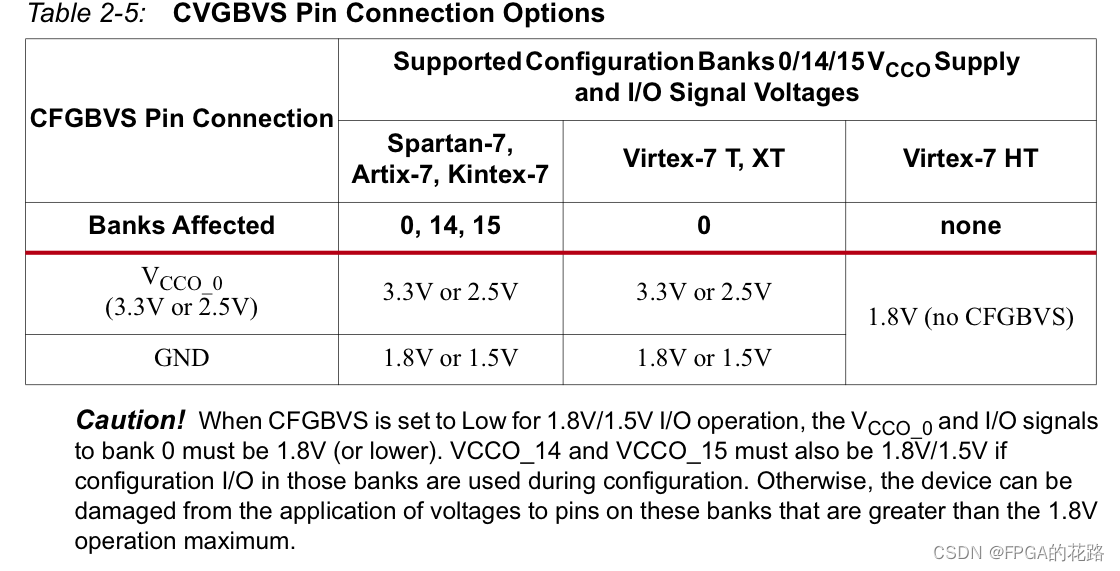

CVGBVS

- иҫ“е…Ҙеј•и„ҡпјӣ

- CVGBVSеҶіе®ҡbank0 I/Oж”ҜжҢҒзҡ„з”өеҺӢеҖјпјҢд»ҘеҸҠй…ҚзҪ®еҢәй—ҙbank14гҖҒbank15зҡ„I/OжүҖж”ҜжҢҒзҡ„з”өеҺӢеҖјпјӣ

- иӢҘI/Oе·ҘдҪңеңЁ1.8VжҲ–иҖ…жӣҙдҪҺз”өеҺӢдёӢпјҢCVGBVSжҺҘGNDпјӣ

- иӢҘI/Oе·ҘдҪңеңЁ2.5V/3.3VдёӢпјҢCVGBVSжҺҘVCCO_0(3.3V/2.5V);

- 7зі»еҲ—жңүдёӨз§ҚI/O bankзұ»еһӢпјҡhigh-range (HR I/O) banks ж”ҜжҢҒ3.3,2.5Vз”өеҺӢж ҮеҮҶпјӣa few lower voltage I/O standards, and high-performance (HP I/O) banks ж”ҜжҢҒ 1.8V жҲ–иҖ…жӣҙдҪҺзҡ„з”өеҺӢж ҮеҮҶпјӣ

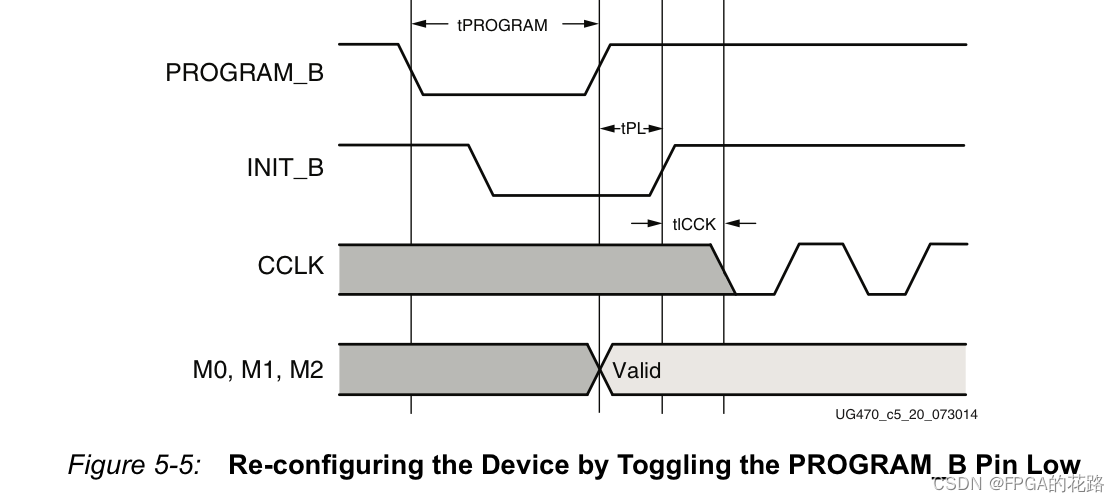

PROGRAM_B

- иҫ“е…Ҙеј•и„ҡпјҢдёӢйҷҚжІҝжңүж•ҲпјҢз”ЁдәҺеӨҚдҪҚж•ҙдёӘеҷЁд»¶пјӣ

- дёҠеҚҮжІҝејҖе§ӢеҗҜеҠЁй…ҚзҪ®пјҢдҪҶдёҠз”өж—¶жҠҠ PROGRAM_B дҝқжҢҒдҪҺз”өе№ідёҚдјҡдҪҝ FPGAй…ҚзҪ®дҝқжҢҒеӨҚдҪҚзҠ¶жҖҒпјҢ延иҝҹй…ҚзҪ®ж—¶й—ҙйңҖиҰҒдҪҝз”Ё INIT_B дҝЎеҸ·й…ҚеҗҲе®ҢжҲҗ

- еј•и„ҡеӨ–йғЁйңҖиҰҒйҖҡиҝҮ4.7kО© д»ҘдёҠз”өйҳ»дёҠжӢүиҮіVCCO_0

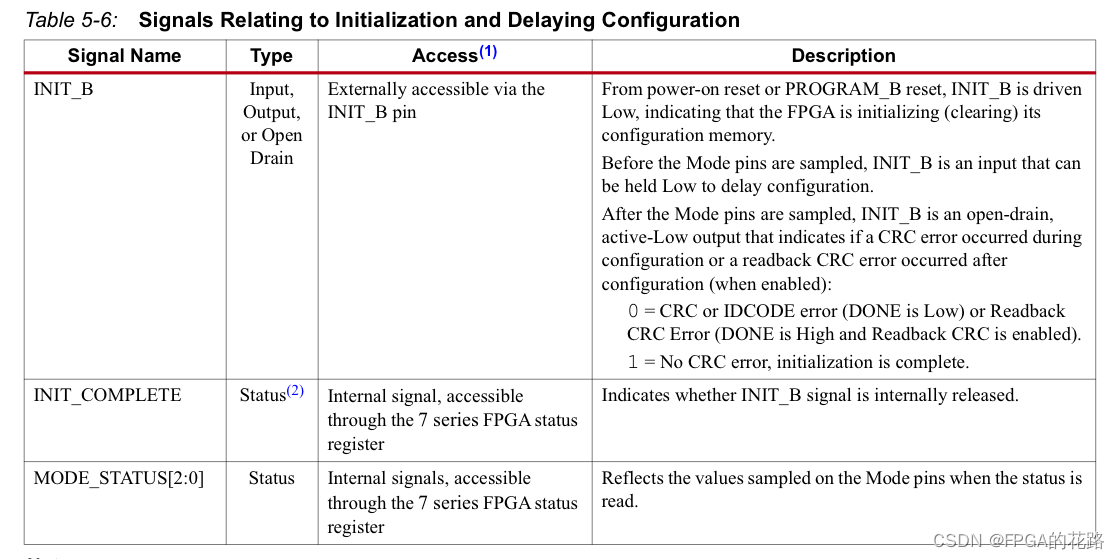

INIT_B

- FPGA еҲқе§ӢеҢ–еј•и„ҡжҲ–й…ҚзҪ®й”ҷиҜҜдҝЎеҸ·,дҪҺз”өе№іжңүж•ҲгҖӮеҪ“ FPGA еӨ„дәҺй…ҚзҪ®еӨҚдҪҚзҠ¶жҖҒжҲ–еҪ“FPGA жӯЈеңЁеҲқе§ӢеҢ–(жё…йҷӨ)е…¶й…ҚзҪ®еӯҳеӮЁеҷЁ(PROGRAM_BдҝЎеҸ·дёәдҪҺз”өе№і)ж—¶жҲ–еҪ“ FPGA жЈҖжөӢеҲ°й…ҚзҪ®й”ҷиҜҜж—¶,FPGA дјҡе°ҶиҜҘеј•и„ҡй©ұеҠЁдёәдҪҺз”өе№іпјӣ

- еңЁдёҠз”өжңҹй—ҙ,еҸҜд»ҘйҖҡиҝҮи®ІиҜҘеј•и„ҡжӢүдҪҺ,жқҘ延иҝҹдёҠз”өй…ҚзҪ®зЁӢеәҸзҡ„ж—¶й—ҙ пјӣ

- еҪ“е®ҢжҲҗеҲқе§ӢеҢ–еҗҺ,иҜҘеј•и„ҡиў«йҮҠж”ҫ,еӨ–йғЁдёҠжӢүз”өйҳ»и®ІиҜҘеј•и„ҡжӢүй«ҳ,еҪ“жЈҖжөӢеҲ°иҜҘдҝЎеҸ·дёҠеҚҮжІҝд№ӢеҗҺ,FPGAдјҡиҜ»еҸ–M[2:0]еј•и„ҡзҠ¶жҖҒ,д»ҺиҖҢзЎ®е®ҡеҗҺз»ӯйҮҮз”Ёе“Әз§Қй…ҚзҪ®ж–№ејҸиҝӣиЎҢй…ҚзҪ® пјӣ

- еј•и„ҡеӨ–йғЁйңҖиҰҒйҖҡиҝҮ4.7KО©д»ҘдёҠзҡ„з”өйҳ»дёҠжӢүиҮіVCCO_0 пјӣ

- M[2:0]иў«йҮҮж ·д№ӢеҗҺпјҡINIT_BдҪңдёәиҫ“еҮәпјҢ0иЎЁзӨәCRCжҲ–IDCODEй”ҷиҜҜпјҲиҝҷж—¶DONEдёәдҪҺз”өе№іпјүпјҢ0жҲ–иЎЁзӨәеӣһиҜ»CRCй”ҷиҜҜпјҲиҝҷж—¶DONEдёәй«ҳз”өе№іпјҢдё”еӣһиҜ»CRCдҪҝиғҪпјүпјӣ1иЎЁзӨәжІЎжңүCRCй”ҷиҜҜпјҢеҲқе§ӢеҢ–е®ҢжҲҗ

PUDC_B

- иҫ“е…Ҙеј•и„ҡпјҲдёҚеҸҜжӮ¬з©әпјүпјҢеңЁй…ҚзҪ®жңҹй—ҙI/Oеј•и„ҡеҶ…йғЁдёҠжӢүз”өйҳ»дҪҝиғҪпјӣ

- дҪҺз”өе№іпјҢй…ҚзҪ®жңҹй—ҙжүҖжңүжңӘиөӢеҖјеј•и„ҡдёәй«ҳз”өе№іпјӣ

- й«ҳз”өе№іпјҢй…ҚзҪ®жңҹй—ҙжүҖжңүжңӘиөӢеҖјеј•и„ҡдёәй«ҳйҳ»жҖҒ

VCCBATT

- FPGAеҶ…йғЁжҳ“еӨұжҖ§еӯҳеӮЁеҷЁзҡ„з”өжұ еӨҮз”Ёз”өжәҗ,з”ЁдәҺеӯҳеӮЁAESи§ЈеҜҶеҷЁзҡ„еҜҶй’Ҙ,еҰӮжһңдёҚйңҖиҰҒдҪҝз”ЁAESжҳ“еӨұжҖ§еҜҶй’ҘеӯҳеӮЁеҢәеҹҹдёӯзҡ„и§ЈеҜҶеҷЁеҜҶй’Ҙ,йӮЈд№Ҳе°ҶиҜҘеј•и„ҡжҺҘең°е°ұиЎҢ,иҜҘеј•и„ҡдёҚжҳҜI/O,дёҚеҸ—VCCO_0зҡ„еҪұе“Қ

RS0, RS1

- иҫ“еҮәеј•и„ҡпјҢRS[1:0]з”ЁеӨҡй•ңеғҸй…ҚзҪ®пјҲMultiBootпјү

RDWR_B

- иҫ“е…Ҙеј•и„ҡпјӣ

- й«ҳз”өе№іпјҡFPGAиҫ“еҮәж•°жҚ®еҲ°SelectMapж•°жҚ®зәҝдёҠпјӣ

- дҪҺз”өе№іпјҡеӨ–йғЁжҺ§еҲ¶еҷЁйҖҡиҝҮSelectMapж•°жҚ®зәҝеҶҷж•°жҚ®еҲ°FPGA

FCS_B

- иҫ“еҮәеј•и„ҡпјҢflashзүҮйҖүдҝЎеҸ·пјҢдҪҺжңүж•Ҳ

FOE_B

- иҫ“еҮәеј•и„ҡпјҢflashиҫ“еҮәдҪҝиғҪпјҢдҪҺжңүж•Ҳ

FWE_B

- иҫ“еҮәеј•и„ҡпјҢflashеҶҷдҪҝиғҪпјҢдҪҺжңүж•Ҳ

Configuration Details

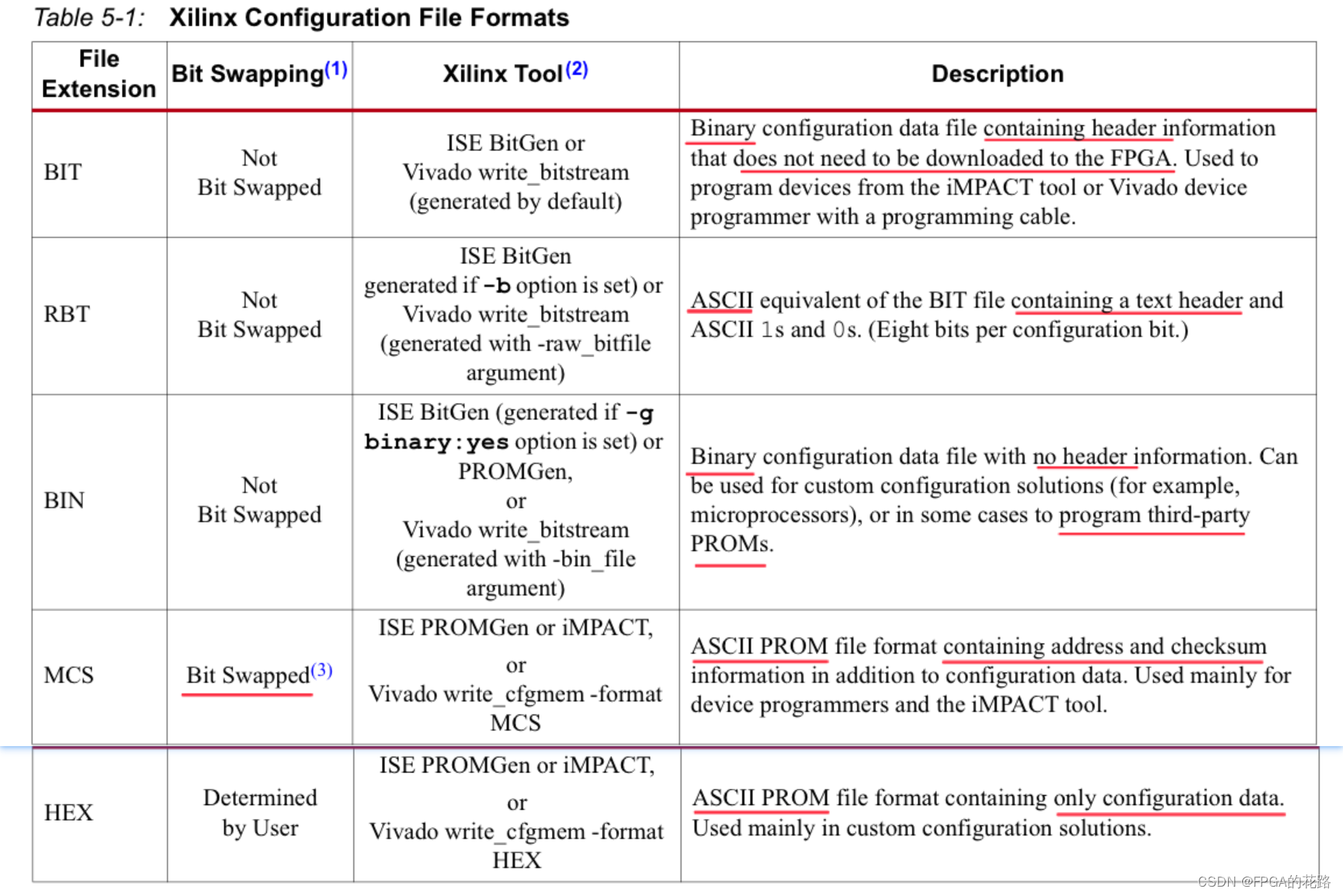

й…ҚзҪ®ж–Үд»¶ж јејҸ

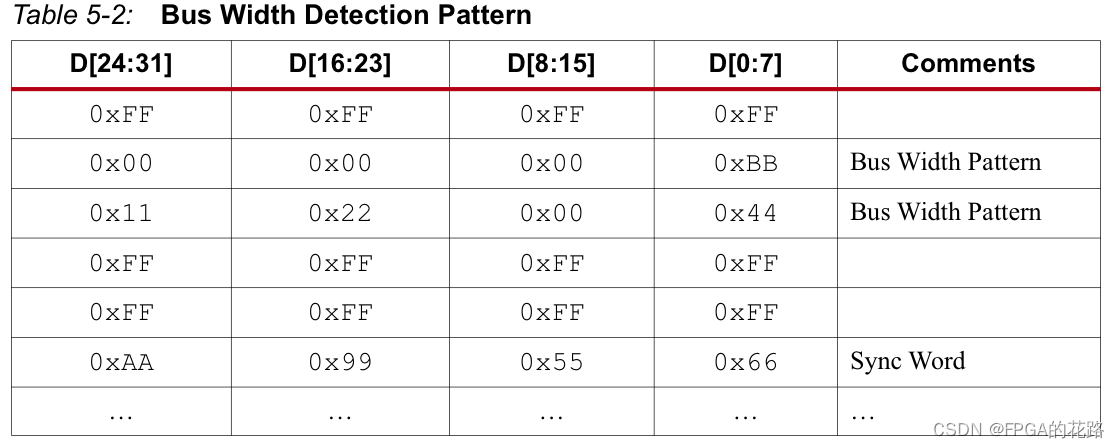

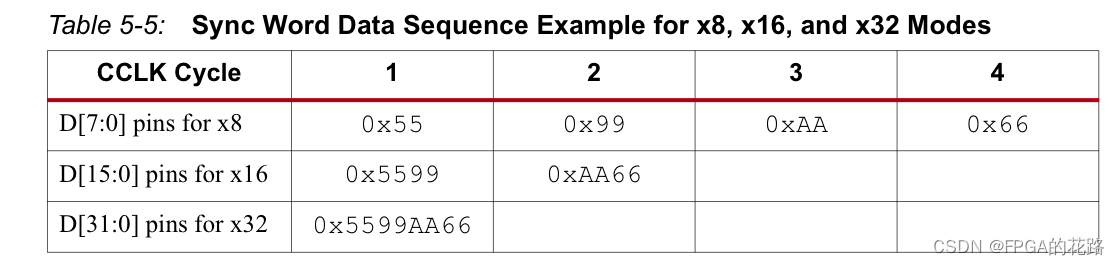

жҖ»зәҝдҪҚе®ҪиҮӘеҠЁжЈҖжөӢ

- SerialгҖҒJTAGгҖҒSPIжЁЎејҸдёҚж”ҜжҢҒжҖ»зәҝдҪҚе®ҪиҮӘеҠЁжЈҖжөӢеҠҹиғҪпјӣ

- еҸӘжЈҖжөӢD[7:0]зҡ„еҖјпјҢжЈҖжөӢеҲ°0xBBпјҢиӢҘдёӢдёҖж¬ЎжЈҖжөӢеҲ°0x11пјҢеҲҷдёәx8пјӣиӢҘдёӢдёҖж¬ЎжЈҖжөӢеҲ°0x22пјҢеҲҷдёәx16пјӣиӢҘдёӢдёҖж¬ЎжЈҖжөӢеҲ°0x44пјҢеҲҷдёәx32пјӣ然еҗҺз«ӢеҚіеҲҮжҚўжҖ»зәҝдҪҚе®ҪпјҢејҖе§ӢжЈҖжөӢеҗҢжӯҘеӯ—

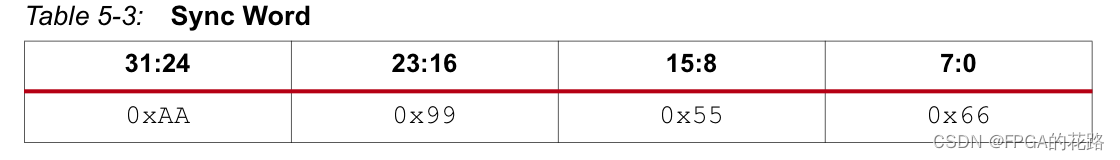

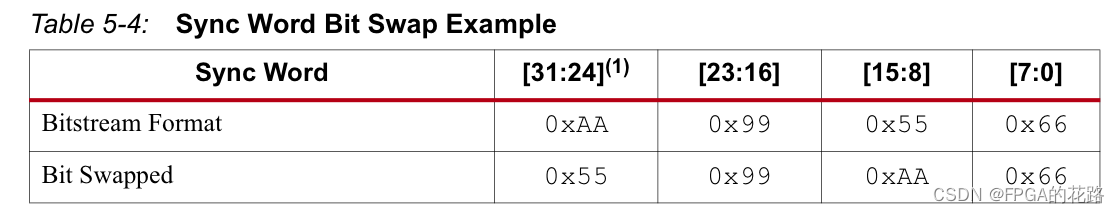

еҗҢжӯҘеӯ—

- иҜҶеҲ«еҲ°еҗҢжӯҘеӯ—еүҚжІЎжңүе…¶д»–еҢ…ж•°жҚ®

дҪҚдәӨжҚўе’ҢжҖ»зәҝеӯ—еәҸ

延иҝҹй…ҚзҪ®

- йҖҡиҝҮ INIT_BдҝқжҢҒдҪҺз”өе№іжқҘ延иҝҹй…ҚзҪ®гҖӮеҪ“INIT_BжӢүй«ҳеҗҺпјҲе®ҢжҲҗеҲқе§ӢеҢ–йҳ¶ж®өпјүпјҢеҶҚж¬ЎжӢүдҪҺдёҚдјҡ延иҝҹй…ҚзҪ®гҖӮ

延иҝҹзӣёе…ідҝЎеҸ·

й…ҚзҪ®йЎәеәҸ

Setup

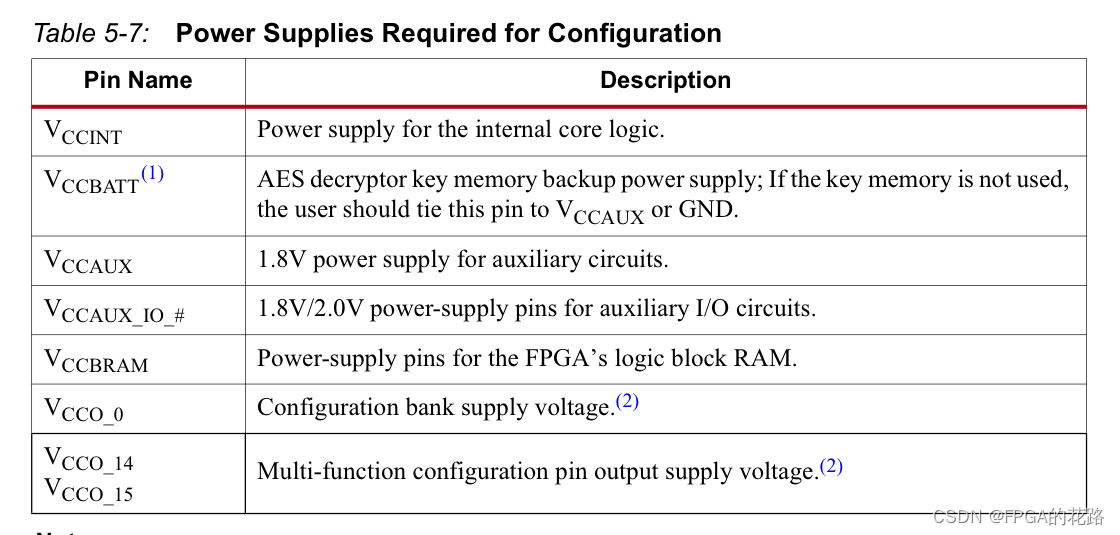

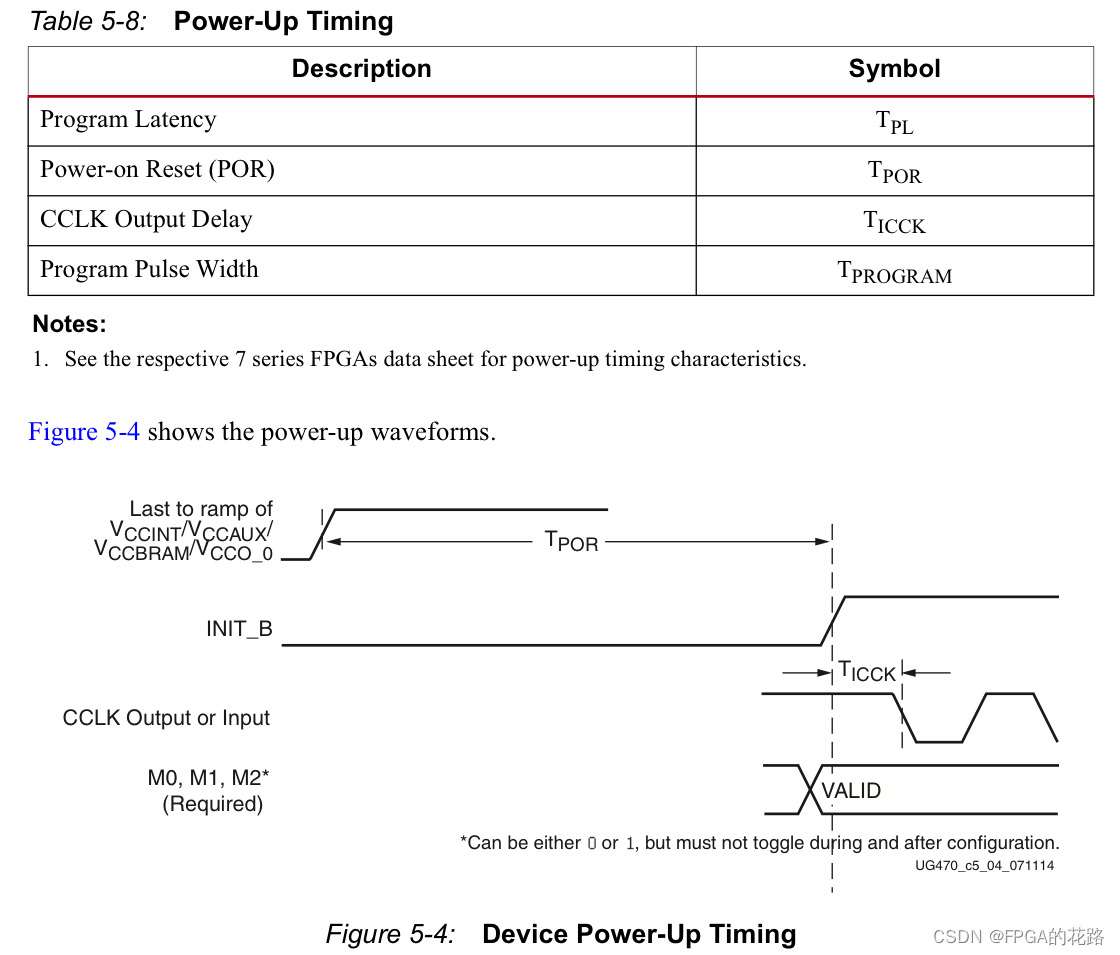

Device Power-Up (Step 1)

- з”өжәҗеј•и„ҡ

- дёҠз”өж—¶еәҸ

Clear Configuration Memory (Step 2, Initialization)

- д»ҘдёӢжғ…еҶөйғҪдјҡи§ҰеҸ‘вҖңжё…йҷӨй…ҚзҪ®еӯҳеӮЁвҖқпјҡйҮҚж–°дёҠз”өгҖҒPROGRAM_BдҪҺи„үеҶІгҖҒJTAG JPROGRAMжҢҮд»ӨгҖҒIPROGжҢҮд»ӨгҖҒfallbackйҮҚй…ҚзҪ®пјӣ

- BRAMе’ҢеҜ„еӯҳеҷЁйғҪдјҡйҖҡиҝҮGSRжӢүй«ҳеҲқе§ӢеҢ–пјӣ

- иҝҷж®өжңҹй—ҙпјҢйҷӨдәҶе°‘ж•°й…ҚзҪ®иҫ“еҮәеј•и„ҡпјҢе…¶д»–I/OйҖҡиҝҮGTSеӨ„дәҺй«ҳйҳ»жҖҒпјҢеҰӮжһңPUDC_BдёәдҪҺпјҢеҲҷдёәеҶ…йғЁдёҠжӢү

Sample Mode Pins (Step 3)

- INIT_BжӢүй«ҳеҗҺпјҢеҷЁд»¶йҮҮйӣҶM[2:0]жЁЎејҸеј•и„ҡеҖјпјҢй©ұеҠЁCCLKпјҲmasterжЁЎејҸдёӢпјүпјҢ然еҗҺеңЁCCLKдёҠеҚҮжІҝйҮҮйӣҶй…ҚзҪ®ж•°жҚ®еј•и„ҡеҖј

Bitstream Loading

Synchronization (Step 4)

- еҜ№дәҺBPIжЁЎејҸгҖҒSelectMAPжЁЎејҸпјҢеҗҢжӯҘеүҚйңҖиҰҒе…ҲиҮӘеҠЁиҜҶеҲ«дҪҚе®Ҫпјӣ

- д»»дҪ•еҗҢжӯҘеӯ—еүҚзҡ„ж•°жҚ®йғҪдјҡиў«еҝҪз•ҘпјҢйҷӨдәҶдҪҚе®ҪжЈҖжөӢеәҸеҲ—пјӣ

- еҗҢжӯҘйҳ¶ж®өеҜ№дәҺеӨ§еӨҡж•°з”ЁжҲ·жҳҜйҖҸжҳҺзҡ„пјҢеӣ дёәе·Ҙе…·з”ҹжҲҗзҡ„bitеҢ…еҗ«дҪҚе®ҪжЈҖжөӢеәҸеҲ—еҸҠеҗҢжӯҘеӯ—

еҗҢжӯҘйҳ¶ж®өзӣёе…ідҝЎеҸ·

Check Device ID (Step 5)

-

еҗҢжӯҘд№ӢеҗҺиҝӣиЎҢеҷЁд»¶IDжЈҖйӘҢпјҢеҰӮжһңIDдёҚеҢ№й…ҚеҲҷеӣһйҖҖиҝӣиЎҢйҮҚй…ҚзҪ®

-

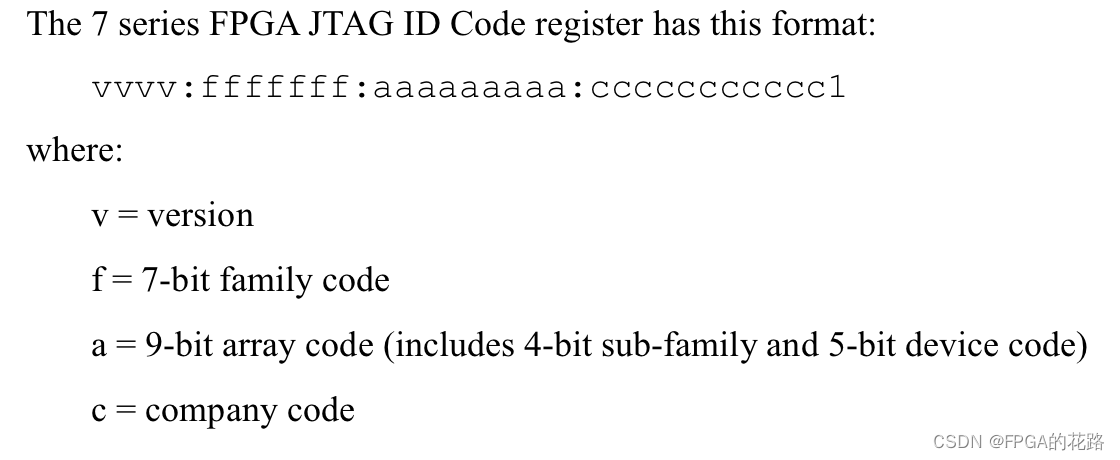

7зі»еҲ— jtag ID CodeеҜ„еӯҳеҷЁж јејҸ

Load Configuration Data Frames (Step 6)

- еҗҢжӯҘеӯ—еҠ иҪҪеҸҠеҷЁд»¶IDжЈҖжҹҘе®ҢжҲҗеҗҺпјҢејҖе§ӢеҠ иҪҪй…ҚзҪ®ж•°жҚ®её§

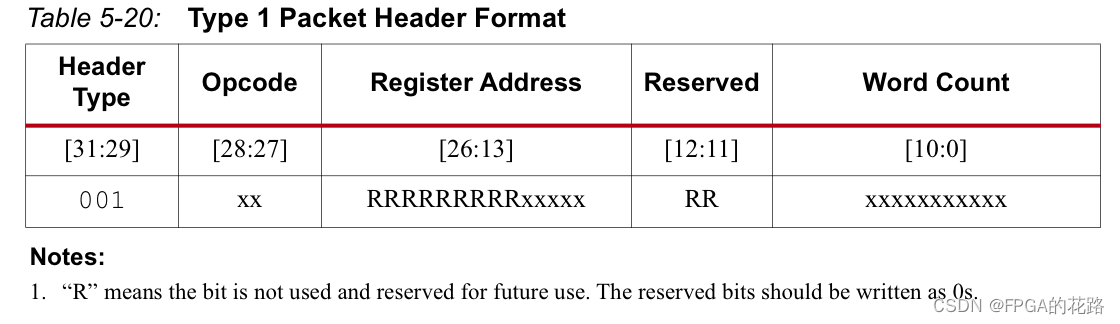

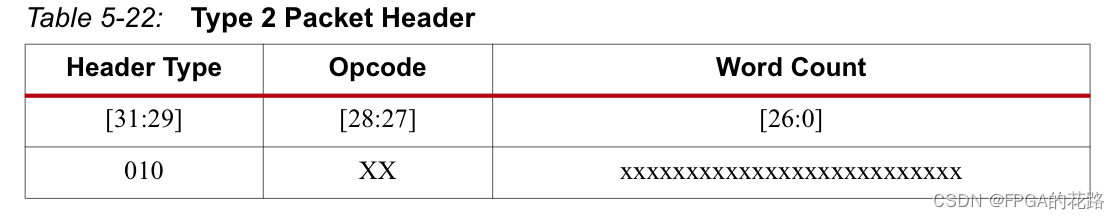

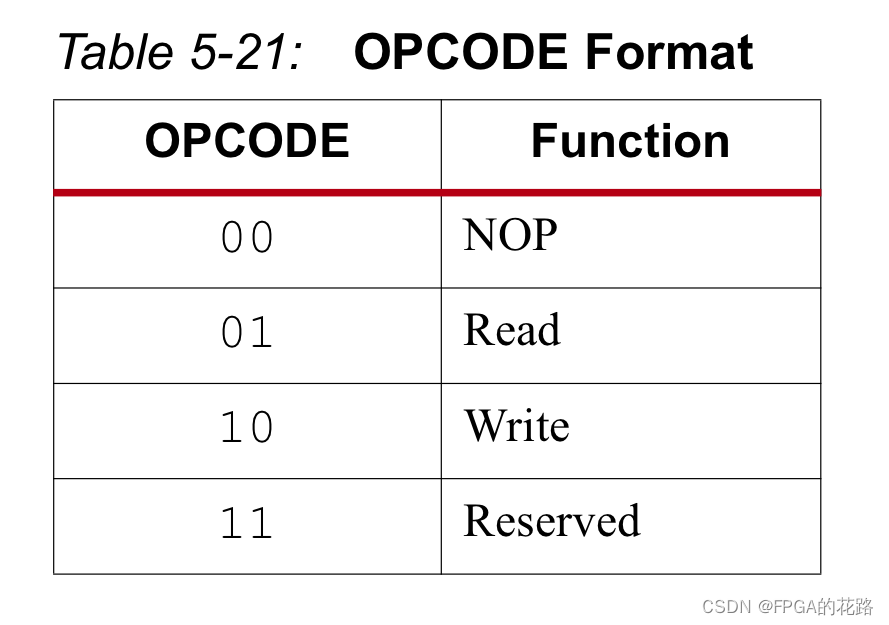

- Configuration Packets пјҡType1гҖҒType2дёӨз§ҚпјҢеҜ„еӯҳеҷЁең°еқҖеҸӘз”Ё5bit

Cyclic Redundancy Check (Step 7)

- FPGA и®Ўз®—CRCи·ҹbitйҮҢзҡ„ж ЎйӘҢеҖјжҜ”иҫғпјӣ

- еҗҢжӯҘдёўеӨұеҗҺпјҢеҗҺз»ӯзҡ„жҢҮд»ӨйғҪиў«еҝҪз•ҘпјҢжңҖй…ҚзҪ®еӨұиҙҘвҖ”DONEдҪҺпјҢINIT_Bй«ҳ

Startup

- DONEзҪ®дҪҚеҗҺиҰҒдҝқз•ҷи¶іеӨҹж—¶й—ҙдҝқиҜҒиғҪеҲ° phase7пјҢдҝқе®Ҳж—¶й—ҙдёә64дёӘж—¶й’ҹе‘Ёжңҹ

- йҳІжӯўDONEгҖҒGTSгҖҒGWEеңЁMMCMsй”Ғзӣёе’ҢDCIеҢ№й…ҚеүҚзҪ®дҪҚ

й…ҚзҪ®иҝҮзЁӢI/Oз”өе№іеҸҳеҢ–пјҲEOSпјү

- еңЁEnd Of StartupеҗҺдёҖдёӘCFGCLKеҸ‘з”ҹ0-1-0зҡ„з”өе№іиҪ¬еҸҳиҝҮзЁӢпјӣ

- йҒҝе…Қдә§з”ҹеҪұе“ҚпјҡVCCO14гҖҒ15жҺҘ2.5/3.3VпјӣжҲ–иҖ…еӨ–йғЁеј•и„ҡдёҠжӢүпјӣиҝҳеҸҜд»ҘйҖ»иҫ‘и®ҫи®ЎеҝҪз•ҘEOS еҗҺ第дёҖдёӘCFGCLKдёҠеҚҮжІҝд№ӢеҗҺиҮіе°‘200nsдёҚйҮҮзәіж•°жҚ®

STARTUPE2еҺҹиҜӯ

Bitstream Security

Bitstream Composition

й…ҚзҪ®еҜ„еӯҳеҷЁ

йҮҚй…ҚзҪ®е’ҢеӨҡй•ңеғҸ

Fallback MultiBoot

- еӣһйҖҖеҠҹиғҪдҪҝиғҪпјҡConfigFallbackпјҲйҖҡиҝҮxdcзәҰжқҹжҲ–иҖ…bitstreamи®ҫзҪ®пјүпјӣ

- еӣһйҖҖйҮҚй…ҚзҪ®ж—¶е°ҶеҝҪз•ҘIPROGпјҢзңӢй—ЁзӢ—и®Ўж—¶еҷЁе…ій—ӯпјӣ

- йҮҚй…ҚзҪ®еӨұиҙҘпјҢй…ҚзҪ®з»ҲжӯўпјҢINIT_Bе’ҢDONEдҝқжҢҒдҪҺз”өе№і

е…ҲеҠ иҪҪgoldenеҶҚи§ҰеҸ‘MultiBoot

зӣҙжҺҘеҠ иҪҪMultiBoot

- еҜ№дәҺSPIжЁЎејҸпјҢеӣһйҖҖй»ҳи®ӨдҪҝз”Ёx1иҝӣиЎҢgoldenй•ңеғҸеҠ иҪҪпјӣ

- еҜ№дәҺBPIжЁЎејҸпјҢеӣһйҖҖй»ҳи®ӨдҪҝз”ЁејӮжӯҘиҜ»жЁЎејҸиҝӣиЎҢй•ңеғҸеҠ иҪҪпјҢжүҖд»ҘеҪ“й…ҚзҪ®дёәеҗҢжӯҘиҜ»жЁЎејҸж—¶иҰҒжіЁж„ҸCCLKпјҢеҗҢж—¶иҰҒж»Ўи¶іејӮжӯҘе’ҢеҗҢжӯҘиҜ»жЁЎејҸпјӣ

- BPIжЁЎејҸпјҢ硬件и®ҫи®ЎRSеј•и„ҡиҰҒж №жҚ®upper addressиҝӣиЎҢдёҠжӢүжҲ–иҖ…дёӢжӢү

IPROG

- IPROGпјҲInternal PROGRAMпјүжҢҮд»Өе’ҢPROGRAM_Bеј•и„ҡз»ҷдҪҺи„үеҶІдҪңз”Ёзұ»дјјпјҢеҢәеҲ«еңЁдәҺIPROGдёҚеӨҚдҪҚWBSTARгҖҒTIMERгҖҒBSPIе’ҢBOOTSTSеҜ„еӯҳеҷЁеҖјпјӣ

- IPROGжҢҮд»Өи§ҰеҸ‘еҲқе§ӢеҢ–пјҢеҗҢж—¶INITе’ҢDONEжӢүдҪҺпјӣ

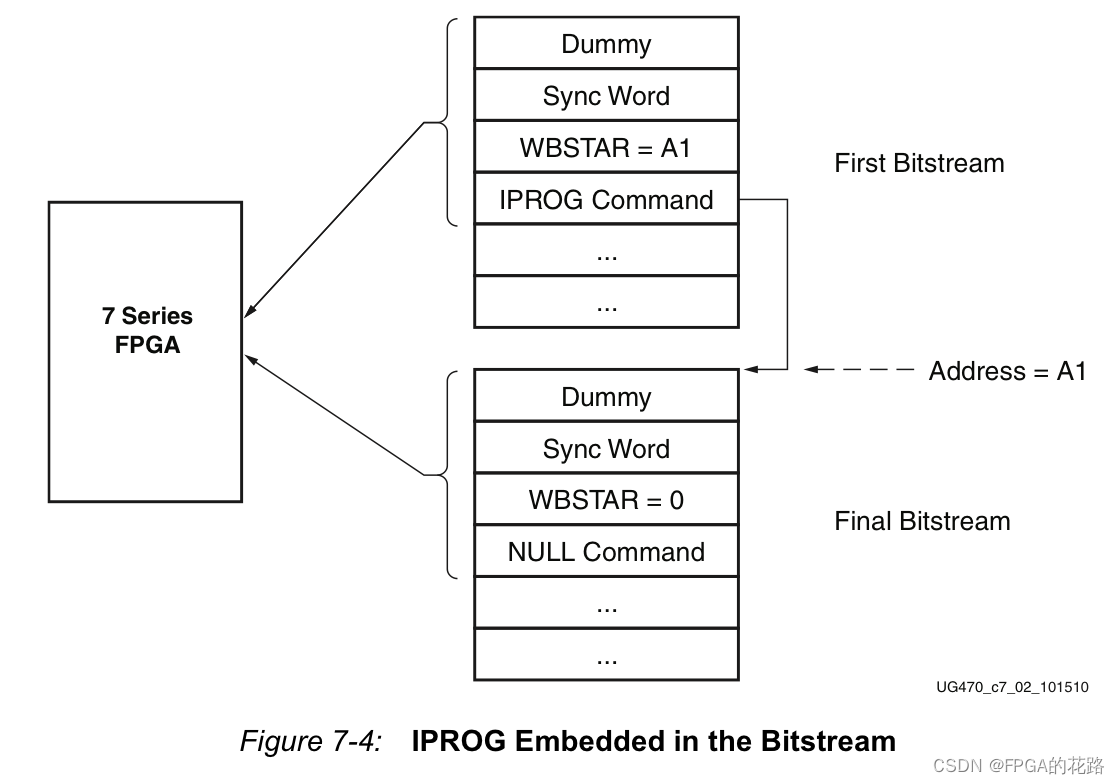

- дёӨз§ҚеҸ‘иө·жҢҮд»Өж–№ејҸпјҡйҖ»иҫ‘жҺ§еҲ¶ICAPE2пјӣз”ҹжҲҗbitж—¶еңЁgolden bitеүҚеҠ е…ҘWBSTARе’ҢIPROGжҢҮд»Өпјӣ 4.еҪ“и§ҰеҸ‘еӣһйҖҖйҮҚж–°еҠ иҪҪж—¶IPROGжҢҮд»Өе°Ҷиў«еҝҪз•Ҙ

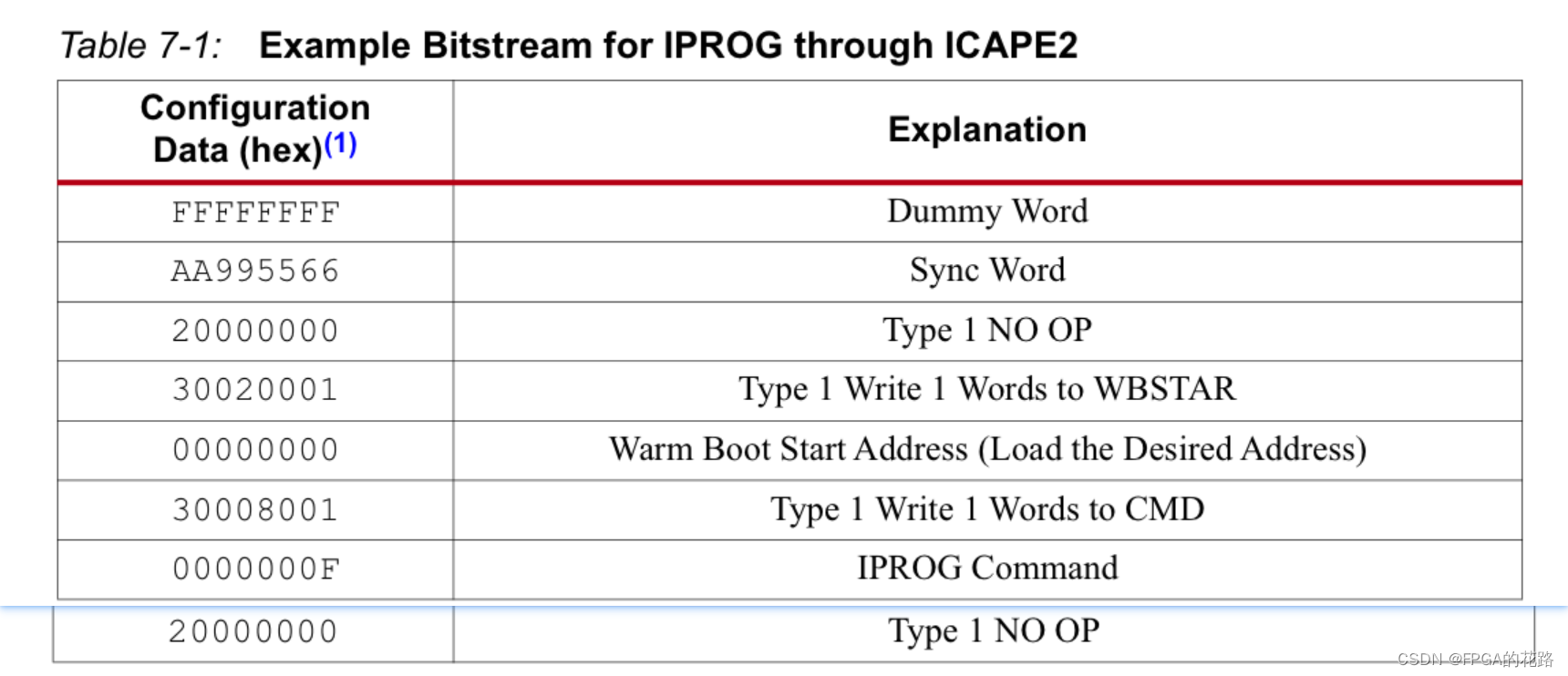

IPROG Using ICAPE2

- иҫ“е…Ҙй…ҚзҪ®дҝЎжҒҜйңҖиҰҒдҪҚиҪ¬жҚўпјӣ

- еҸ‘йҖҒжөҒзЁӢпјҡеҗҢжӯҘеӯ—->WBSTAR->IPROG

IPROG Embedded in the Bitstream

Status Register for Fallback and IPROG Reconfiguration

- BOOTSTSз”ЁдәҺеӯҳеӮЁй…ҚзҪ®еҺҶеҸІпјӣ

- Validз”ЁдәҺеҸӘжҳҜеҪ“еүҚStatusжҳҜеҗҰжңүж•Ҳпјӣ

- Status_0з”ЁдәҺи®°еҪ•жңҖж–°й…ҚзҪ®зҠ¶жҖҒпјӣ Status_1з”ЁдәҺи®°еҪ•дёҠдёҖж¬Ўй…ҚзҪ®зҠ¶жҖҒпјӣ

- Status_1 иЎЁзӨәжү§иЎҢдәҶIPROGпјҢжЈҖжөӢеҲ°CRCй”ҷиҜҜпјӣ

- Status_0иЎЁзӨәеӣһйҖҖеҠ иҪҪжҲҗеҠҹпјҢеҗҢж—¶д№ҹжңүIPROGпјҢеҸӘжҳҜеӣһйҖҖйҮҚй…ҚзҪ®еҝҪз•ҘIPROGжҢҮд»ӨпјҢдҪҶжҳҜеҗҢж ·и®°еҪ•зҠ¶жҖҒ

WBSTAR Register

- жү§иЎҢIPROGжҢҮд»ӨеҗҺпјҢFPGAд»ҺWBSTARжҢҮзӨәзҡ„ең°еқҖејҖе§ӢиҜ»жҢҮд»Ө

Watchdog Timer

- дёӨз§ҚжЁЎејҸпјҡй…ҚзҪ®зӣ‘жҺ§гҖҒз”ЁжҲ·йҖ»иҫ‘зӣ‘жҺ§пјӣ

- и®Ўж•°еҲ°иҫҫ0пјҢи§ҰеҸ‘еӣһйҖҖпјӣ

- и®Ўж—¶еҷЁеҜ„еӯҳеҷЁи®Ўж•°ж—¶й’ҹдёәCFGMCLKпјҲ65MHzпјүпјү256еҲҶйў‘пјҢдёҖдёӘж—¶й’ҹе‘Ёжңҹдёә4000nsпјҢи®Ўж•°еҷЁдҪҚе®Ҫ30bitsпјҢжүҖд»ҘеҸҜд»Ҙи®Ўж—¶4230з§’пјӣ

- еӣһйҖҖйҮҚй…ҚзҪ®ж—¶пјҢWatchdogдёҚдҪҝиғҪ

Configuration Monitor Mode

- TIMERеҜ„еӯҳеҷЁпјҡTIME_CFG_MONи®ҫдёә1пјҢ并и®ҫзҪ®и¶…ж—¶и®Ўж•°еҖј

User Monitor Mode

- TIMERеҜ„еӯҳеҷЁпјҡTIME_USR_MONи®ҫдёә1пјҢ并и®ҫзҪ®и¶…ж—¶и®Ўж•°еҖј

RS Pins

-

йҷӨSPIй…ҚзҪ®жЁЎејҸпјҢRSдҝЎеҸ·еқҮз”ұWBSTARеҜ„еӯҳеҷЁжҺ§еҲ¶иҫ“еҮәпјӣ

-

еҪ“BPIжҲ–Master SelectMapжЁЎејҸеӣһйҖҖж—¶пјҢиҫ“еҮәдҪҺз”өе№іпјӣ

-

еңЁеӨҡй•ңеғҸеңәжҷҜз”ЁдҪңдёәй«ҳдҪҚең°еқҖзәҝпјӣ

-

йҷӨCCLKеӨ–жүҖжңүBPIеј•и„ҡеқҮдёәеӨҡеҠҹиғҪI/OпјҢй…ҚзҪ®е®ҢжҲҗеҗҺпјҲDONEдёәй«ҳпјүеқҮеҸҜз”ұз”ЁжҲ·жҺ§еҲ¶

JTAGй«ҳзә§з”Ёжі•

еҸӮиҖғж–ҮзҢ®

7 Series FPGAs Configuration User Guide (UG470)

-

- TIMERеҜ„еӯҳеҷЁпјҡTIME_USR_MONи®ҫдёә1пјҢ并и®ҫзҪ®и¶…ж—¶и®Ўж•°еҖј

- TIMERеҜ„еӯҳеҷЁпјҡTIME_CFG_MONи®ҫдёә1пјҢ并и®ҫзҪ®и¶…ж—¶и®Ўж•°еҖј

- жү§иЎҢIPROGжҢҮд»ӨеҗҺпјҢFPGAд»ҺWBSTARжҢҮзӨәзҡ„ең°еқҖејҖе§ӢиҜ»жҢҮд»Ө

- йҳІжӯўDONEгҖҒGTSгҖҒGWEеңЁMMCMsй”Ғзӣёе’ҢDCIеҢ№й…ҚеүҚзҪ®дҪҚ

- DONEзҪ®дҪҚеҗҺиҰҒдҝқз•ҷи¶іеӨҹж—¶й—ҙдҝқиҜҒиғҪеҲ° phase7пјҢдҝқе®Ҳж—¶й—ҙдёә64дёӘж—¶й’ҹе‘Ёжңҹ

- Configuration Packets пјҡType1гҖҒType2дёӨз§ҚпјҢеҜ„еӯҳеҷЁең°еқҖеҸӘз”Ё5bit

- еҗҢжӯҘеӯ—еҠ иҪҪеҸҠеҷЁд»¶IDжЈҖжҹҘе®ҢжҲҗеҗҺпјҢејҖе§ӢеҠ иҪҪй…ҚзҪ®ж•°жҚ®её§

-

- INIT_BжӢүй«ҳеҗҺпјҢеҷЁд»¶йҮҮйӣҶM[2:0]жЁЎејҸеј•и„ҡеҖјпјҢй©ұеҠЁCCLKпјҲmasterжЁЎејҸдёӢпјүпјҢ然еҗҺеңЁCCLKдёҠеҚҮжІҝйҮҮйӣҶй…ҚзҪ®ж•°жҚ®еј•и„ҡеҖј

- дёҠз”өж—¶еәҸ

- з”өжәҗеј•и„ҡ

- йҖҡиҝҮ INIT_BдҝқжҢҒдҪҺз”өе№іжқҘ延иҝҹй…ҚзҪ®гҖӮеҪ“INIT_BжӢүй«ҳеҗҺпјҲе®ҢжҲҗеҲқе§ӢеҢ–йҳ¶ж®өпјүпјҢеҶҚж¬ЎжӢүдҪҺдёҚдјҡ延иҝҹй…ҚзҪ®гҖӮ

- иҜҶеҲ«еҲ°еҗҢжӯҘеӯ—еүҚжІЎжңүе…¶д»–еҢ…ж•°жҚ®

- иҫ“еҮәеј•и„ҡпјҢflashеҶҷдҪҝиғҪпјҢдҪҺжңүж•Ҳ

- иҫ“еҮәеј•и„ҡпјҢflashиҫ“еҮәдҪҝиғҪпјҢдҪҺжңүж•Ҳ

- иҫ“еҮәеј•и„ҡпјҢflashзүҮйҖүдҝЎеҸ·пјҢдҪҺжңүж•Ҳ

- иҫ“еҮәеј•и„ҡпјҢRS[1:0]з”ЁеӨҡй•ңеғҸй…ҚзҪ®пјҲMultiBootпјү

- FPGAеҶ…йғЁжҳ“еӨұжҖ§еӯҳеӮЁеҷЁзҡ„з”өжұ еӨҮз”Ёз”өжәҗ,з”ЁдәҺеӯҳеӮЁAESи§ЈеҜҶеҷЁзҡ„еҜҶй’Ҙ,еҰӮжһңдёҚйңҖиҰҒдҪҝз”ЁAESжҳ“еӨұжҖ§еҜҶй’ҘеӯҳеӮЁеҢәеҹҹдёӯзҡ„и§ЈеҜҶеҷЁеҜҶй’Ҙ,йӮЈд№Ҳе°ҶиҜҘеј•и„ҡжҺҘең°е°ұиЎҢ,иҜҘеј•и„ҡдёҚжҳҜI/O,дёҚеҸ—VCCO_0зҡ„еҪұе“Қ

- ж— и®әM[2:0]й…ҚзҪ®дёәдҪ•еҖјпјҢйғҪж”ҜжҢҒJTAGеңЁзәҝй…ҚзҪ®

- йҖҡиҝҮCSеҚ•зӢ¬жҺ§еҲ¶жҜҸдёӘеҷЁд»¶

-

-

-

- йҖҡиҝҮдҪҝиғҪ spi_32bit_addr еұһжҖ§ж”ҜжҢҒ32bitең°еқҖжЁЎејҸ

- йҖҡиҝҮspi_buswidthеұһжҖ§ж”№еҸҳиҜ»еҶҷдҪҚе®Ҫ

- жүҖжңүеҷЁд»¶иҰҒдёҖж ·пјҲIDCODEдёҖж ·пјүпјҢй…ҚзҪ®зЁӢеәҸд№ҹдёҖж ·

- йҷӨдәҶCCLK иҝһжҺҘдёҚеҗҢпјҢе…¶д»–йғҪе’Ңд»ҺдёІиЎҢжЁЎејҸдёҖж ·

зӣёе…ійҳ…иҜ»пјҡ